2 hdmi2: analog devices ad8195 buffer – Digilent 210-264P-BOARD User Manual

Page 2

FMC-HDMI Reference Manual

S/PDIF, and Direct Stream Transfer (DST). It also features an advanced mute controller.

The ADV7611 Receiver contains several other features, such as a CEC 1.4-compatible controller for consumer

device remote control and discovery and EDID (Extended Display Identification Data) RAM.

Note: For more information on the ADV7611, see ADI datasheets and User Guide available online at:

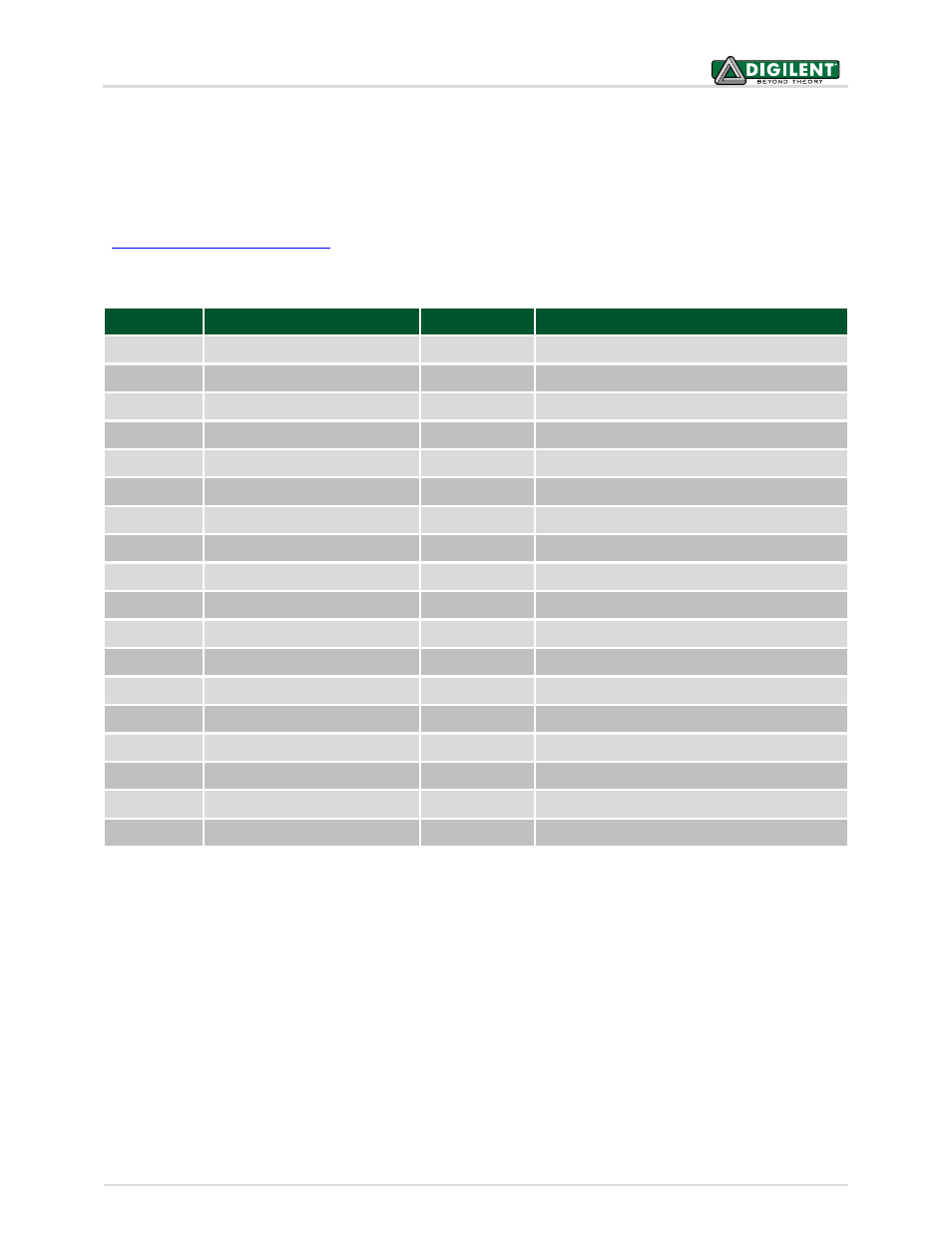

Below are the pin-outs from the ADV7611 Receiver and other HDMI1 port signals to the FMC connector:

FMC Pin

HDMI1 Function

FMC Pin

HDMI1 Function

LA19_P

HDMI1_P0

LA04_P

HDMI1_P18

LA20_N

HDMI1_P1

LA03_N

HDMI1_P19

LA20_P

HDMI1_P2

LA03_P

HDMI1_P20

LA15_N

HDMI1_P3

LA02_N

HDMI1_P21

LA14_N

HDMI1_P4

LA02_P

HDMI1_P22

LA15_P

HDMI1_P5

LA00_N_CC

HDMI1_P23

LA16_N

HDMI1_P6

LA18_P_CC

HDMI1_SCLK

LA16_P

HDMI1_P7

LA21_P

HDMI1_LRCLK

LA11_N

HDMI1_P8

LA17_P_CC

HDMI1_MCLK

LA14_P

HDMI1_P9

LA23_N

HDMI1_AP

LA11_P

HDMI1_P10

LA22_P

HDMI1_VS

LA12_N

HDMI1_P11

LA19_N

HDMI1_HS

LA12_P

HDMI1_P12

LA22_N

HDMI1_DE

LA07_N

HDMI1_P13

LA00_P_CC

HDMI1_LLC

LA08_N

HDMI1_P14

LA25_P

HDMI1_SDA

LA07_P

HDMI1_P15

LA21_N

HDMI1_SCL

LA08_P

HDMI1_P16

LA23_P

HDMI1_RESETN

LA04_N

HDMI1_P17

LA25_N

HDMI1_INT1

Table 1. HDMI1-FMC pin mapping.

The ADV7611 is configured and controlled via an I

2

C interface, which is accessible through the HDMI1SDA and

HDMI1SCL pins on the FMC connector. The ADV7611 User Guide specifically describes the different registers and

commands necessary to control the Receiver.

There are level translators present on all audio and video signals, which can level shift to 1.8V, 2.5V, and 3.3V. The

desired level is set by the VADJ voltage level.

2.2 HDMI2: Analog Devices AD8195 Buffer

The AD8195 is an HDMI buffer with equalized TMDS inputs and optionally pre-emphasized TMDS outputs. The

AD8195 includes bidirectional buffering for the DDC bus and bidirectional buffering with integrated pull-up

resistors for the CEC bus. The DDC and CEC buffers are powered independently of the TMDS buffers so that

DDC/CEC functionality can be maintained when the system is powered off.

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 2 of 3