Cypress AutoStore STK17T88 User Manual

32k x 8 autostore™ nvsram with real time clock, Stk17t88, Features

STK17T88

32K x 8 AutoStore™ nvSRAM with

Real Time Clock

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

• 408-943-2600

Document Number: 001-52040 Rev. *A

Revised March 17, 2009

Features

■

nvSRAM Combined With Integrated Real-Time Clock

Functions (RTC, Watchdog Timer, Clock Alarm, Power

Monitor)

■

Capacitor or Battery Backup for RTC

■

25, 45 ns Read Access and R/W Cycle Time

■

Unlimited Read/Write Endurance

■

Automatic Nonvolatile STORE on Power Loss

■

Nonvolatile STORE Under Hardware or Software Control

■

Automatic RECALL to SRAM on Power Up

■

Unlimited RECALL Cycles

■

200K STORE Cycles

■

20-Year Nonvolatile Data Retention

■

Single 3V +20%, -10% Power Supply

■

Commercial and Industrial Temperatures

■

48-pin 300-mil SSOP Package (RoHS-Compliant)

Description

The Cypress STK17T88 combines a 256 Kb nonvolatile static

RAM (nvSRAM) with a full-featured real-time clock in a reliable,

monolithic integrated circuit.

The 256 Kb nvSRAM is a fast static RAM with a nonvolatile

Quantum Trap storage element included with each memory cell.

The SRAM provides the fast access and cycle times, ease of use

and unlimited read and write endurance of a normal SRAM. Data

transfers automatically to the nonvolatile storage cells when

power loss is detected (the STORE operation). On power up,

data is automatically restored to the SRAM (the RECALL

operation). Both STORE and RECALL operations are also

available under software control.

The real time clock function provides an accurate clock with leap

year tracking and a programmable, high accuracy oscillator. The

Alarm function is programmable for one-time alarms or periodic

minutes, hours, or days alarms. There is also a programmable

watchdog timer for processor control.

ROW

D

E

CO

DER

IN

PU

T BU

FFER

S

COLUMN DEC

G

E

W

COLUMN I/O

POWER

CONTROL

HSB

STORE/

RECALL

CONTROL

SOFTWARE

DETECT

A

13

– A

0

STORE

RECALL

DQ

0

DQ

1

DQ

2

DQ

3

DQ

4

DQ

5

DQ

6

DQ

7

V

CC

V

CAP

RTC

MUX

A

14

– A

0

X

1

X

2

INT

V

RTCbat

V

RTCcap

A

5

A

6

A

7

A

8

A

9

A

11

A

12

A

13

A

14

A

0

A

1

A

2

A

3

A

4

A

10

Quantum Trap

512 X 512

STATIC RAM

ARRAY

512 X 512

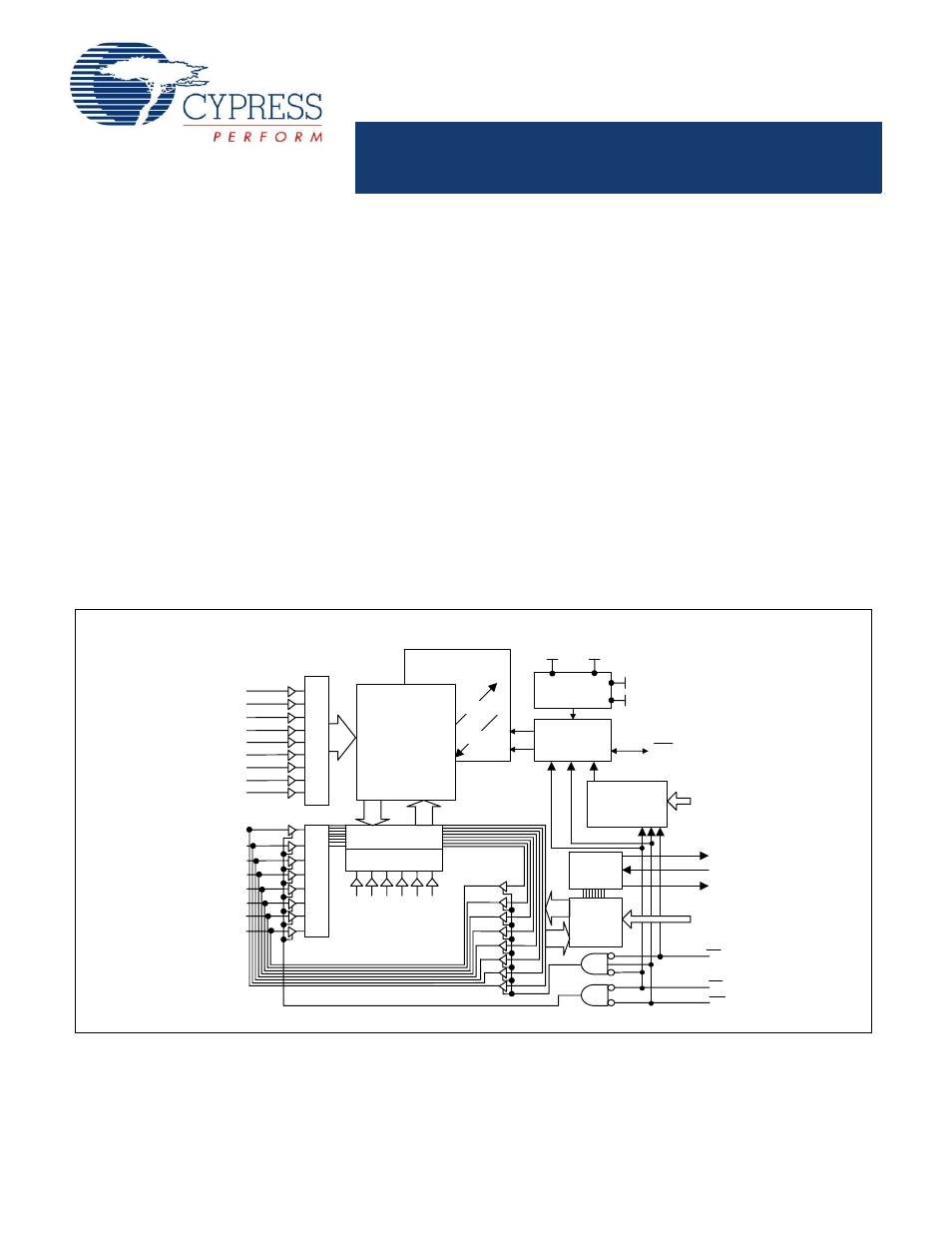

Logic Block Diagram

Document Outline

- Features

- Description

- Logic Block Diagram

- Pin Configurations

- Pin Descriptions

- Absolute Maximum Ratings

- DC Characteristics

- (VCC = 2.7V-3.6V)

- AC Test Conditions

- Capacitance

- RTC DC Characteristics

- SRAM READ Cycles #1 and #2

- SRAM WRITE Cycles #1 and #2

- AutoStore/Power Up RECALL

- Software-Controlled STORE/RECALL Cycle

- Hardware STORE Cycle

- Soft Sequence Commands

- MODE Selection

- nvSRAM Operation

- Real Time Clock

- RTC Register Map

- Commercial and Industrial Ordering Information

- Ordering Codes

- Package Diagram

- Document History Page

- Sales, Solutions, and Legal Information