Switching characteristics – Cypress CY7C1305BV25 User Manual

Page 18

CY7C1307BV25

CY7C1305BV25

Document #: 38-05630 Rev. *A

Page 18 of 21

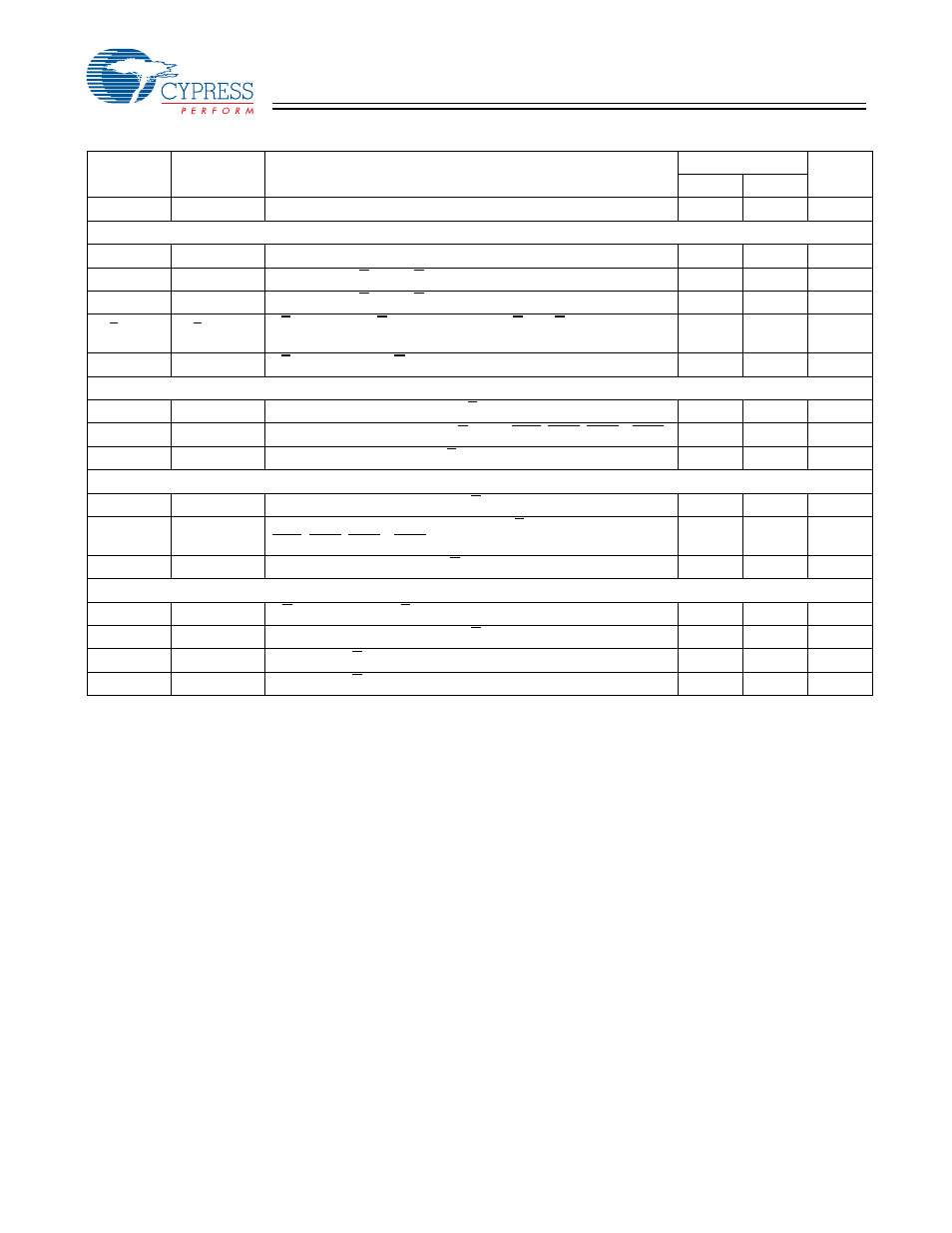

Switching Characteristics

Over the Operating Range

[23]

Cypress

Parameter

Consortium

Parameter

Description

167 MHz

Unit

Min.

Max.

t

Power

[24]

V

CC

(typical) to the First Access Read or Write

10

µs

Cycle Time

t

CYC

t

KHKH

K Clock and C Clock Cycle Time

6.0

ns

t

KH

t

KHKL

Input Clock (K/K and C/C) HIGH

2.4

ns

t

KL

t

KLKH

Input Clock (K/K and C/C) LOW

2.4

ns

t

KHKH

t

KHKH

K/K Clock Rise to K/K Clock Rise and C/C to C/C Rise (rising edge

to rising edge)

2.7

3.3

ns

t

KHCH

t

KHCH

K/K Clock Rise to C/C Clock Rise (rising edge to rising edge)

0.0

2.0

ns

Set-up Times

t

SA

t

SA

Address Set-up to Clock (K and K) Rise

0.7

ns

t

SC

t

SC

Control Set-up to Clock (K and K) Rise (RPS, WPS, BWS

0

, BWS

1

)

0.7

ns

t

SD

t

SD

D

[x:0]

Set-up to Clock (K and K) Rise

0.7

ns

Hold Times

t

HA

t

HA

Address Hold after Clock (K and K) Rise

0.7

ns

t

HC

t

HC

Control Signals Hold after Clock (K and K) Rise

(RPS, WPS, BWS

0

, BWS

1

)

0.7

ns

t

HD

t

HD

D

[x:0]

Hold after Clock (K and K) Rise

0.7

ns

Output Times

t

CO

t

CHQV

C/C Clock Rise (or K/K in single clock mode) to Data Valid

[25]

2.5

ns

t

DOH

t

CHQX

Data Output Hold after Output C/C Clock Rise (Active to Active)

1.2

ns

t

CHZ

t

CHZ

Clock (C and C) rise to High-Z (Active to High-Z)

[25, 26]

2.5

ns

t

CLZ

t

CLZ

Clock (C and C) rise to Low-Z

[25, 26]

1.2

ns

Notes:

23. Unless otherwise noted, test conditions assume signal transition time of 2V/ns, timing reference levels of 0.75V,V

REF

= 0.75V, RQ = 250

Ω

, V

DDQ

= 1.5V, input

pulse levels of 0.25V to 1.25V, and output loading of the specified I

OL

/I

OH

and load capacitance shown in (a) of AC Test Loads.

24. This part has a voltage regulator that steps down the voltage internally; t

Power

is the time power needs to be supplied above V

DD

minimum initially before a Read

or Write operation can be initiated.

25. At any given voltage and temperature t

CHZ

is less than t

CLZ

and, t

CHZ

less than t

CO

.

26. t

CHZ

, t

CLZ

, are specified with a load capacitance of 5 pF as in part (b) of AC Test Loads. Transition is measured ± 100 mV from steady-state voltage.