2 smarc™ connector bottom side, Smarc™ connector bottom side, Smarc-samx6i / connectors – Kontron SMARC-sAMX6i User Manual

Page 26

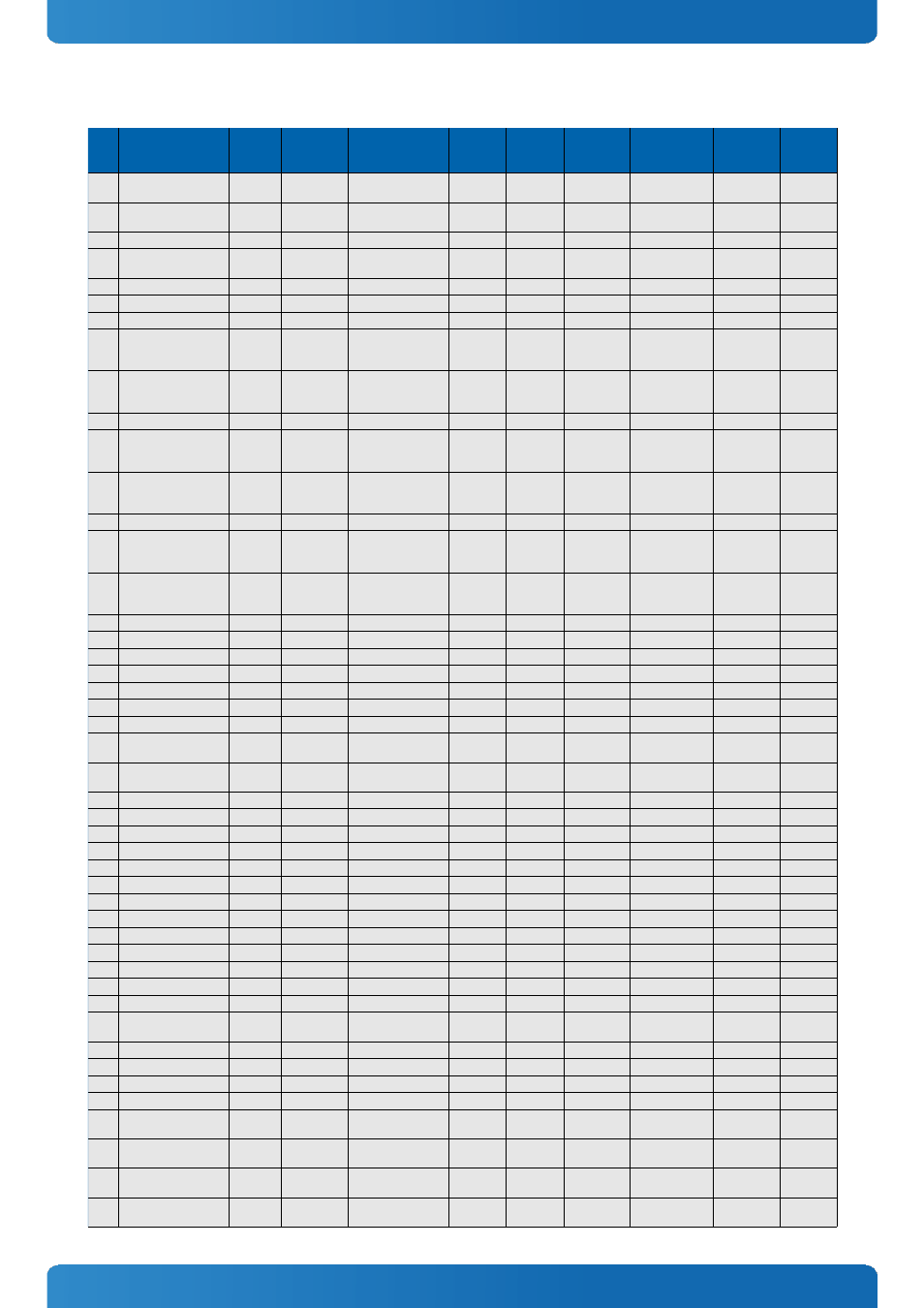

SMARC-sAMX6i / Connectors

4.2

SMARC™ Connector Bottom Side

Pin

Signal

Module

Direction

Module

Termination

Type/Tolerance

Controller Controller

Pin Name

Port(i.MX6

Quad/Dual)

Port(i.MX6

Solo)

I/O MUX

Instance

Quad/Solo

Power Rail

S1

PCAM_VSYNC

In

-

CMOS / VDD_IO

iMX6

EIM_DA12

IPU2_CSI1_

VSYNC

GPIO3_IO12 (*1) ALT2 / ALT5

V_VIO_S0

S2

PCAM_HSYNC

In

-

CMOS / VDD_IO

iMX6

EIM_EB3

IPU2_CSI1_

HSYNC

GPIO2_IO31 (*1) ALT2 / ALT5

V_VIO_S0

S3

GND

-

-

-

-

-

-

-

-

-

S4

PCAM_PXL_CK0

In

-

CMOS / VDD_IO

iMX6

EIM_D17

IPU2_CSI1_

PIXCLK

GPIO3_IO17 (*1) ALT2 / ALT5

V_VIO_S0

S5

I2C_CAM_CK

Out

PU-2k2

CMOS / VDD_IO

iMX6

GPIO_6

GPIO1_IO06

GPIO1_IO06

ALT5 / ALT5

V_VIO_S0

S6

CAM_MCK

Out

-

CMOS / VDD_IO

iMX6

CSI0_MCLK CCM_CLKO1

CCM_CLKO1

ALT3 / ALT3

V_VIO_S0

S7

I2C_CAM_DAT

Bi-Dir

PU-2k2

CMOS / VDD_IO

iMX6

KEY_COL2

GPIO4_IO10

GPIO4_IO10

ALT5 / ALT5

V_VIO_S0

S8

CSI0_CK+ / PCAM_D10 In

-

LVDS D-PHY / VDD_IO iMX6

CSI_CLK0P

-

-

-

V_2V5_VD

DHIGH_CA

P_S0

S9

CSI0_CK- / PCAM_D11

In

-

LVDS D-PHY / VDD_IO iMX6

CSI_CLK0M -

-

-

V_2V5_VD

DHIGH_CA

P_S0

S10

GND

-

-

-

-

-

-

-

-

-

S11

CSI0_D0+ / PCAM_D12 In

-

LVDS D-PHY / VDD_IO iMX6

CSI_D0P

-

-

-

V_2V5_VD

DHIGH_CA

P_S0

S12 CSI0_D0- / PCAM_D13

In

-

LVDS D-PHY / VDD_IO iMX6

CSI_D0M

-

-

-

V_2V5_VD

DHIGH_CA

P_S0

S13 GND

-

-

-

-

-

-

-

-

-

S14 CSI0_D1+ / PCAM_D14 In

-

LVDS D-PHY / VDD_IO iMX6

CSI_D1P

-

-

-

V_2V5_VD

DHIGH_CA

P_S0

S15 CSI0_D1- / PCAM_D15

In

-

LVDS D-PHY / VDD_IO iMX6

CSI_D1M

-

-

-

V_2V5_VD

DHIGH_CA

P_S0

S16

GND

-

-

-

-

-

-

-

-

-

S17

AFB0_OUT

Out

-

CMOS / VDD_IO

-

-

-

-

-

-

S18 AFB1_OUT

Out

-

CMOS / VDD_IO

-

-

-

-

-

-

S19

AFB2_OUT

Out

-

CMOS / VDD_IO

-

-

-

-

-

-

S20

AFB3_IN

In

-

CMOS / VDD_IO

-

-

-

-

-

-

S21

AFB4_IN

In

-

CMOS / VDD_IO

-

-

-

-

-

-

S22

AFB5_IN

In

-

CMOS / VDD_IO

-

-

-

-

-

-

S23

AFB6_PTIO

Bi-Dir

-

CMOS / VDD_IO

protected

iMX6

CSI0_DAT1

8

GPIO6_IO04

GPIO6_IO04

ALT5 / ALT5

V_VIO_S0

S24

AFB7_PTIO

Bi-Dir

-

CMOS / VDD_IO

protected

iMX6

CSI0_DAT1

9

GPIO6_IO05

GPIO6_IO05

ALT5 / ALT5

V_VIO_S0

S25 GND

-

-

-

-

-

-

-

-

-

S26 SDMMC_D0

Bi-Dir

-

CMOS / VDD_IO

iMX6

SD2_DAT0

SD2_DATA0

SD2_DATA0

ALT0 / ALT0

V_VIO_S0

S27 SDMMC_D1

Bi-Dir

-

CMOS / VDD_IO

iMX6

SD2_DAT1

SD2_DATA1

SD2_DATA1

ALT0 / ALT0

V_VIO_S0

S28 SDMMC_D2

Bi-Dir

-

CMOS / VDD_IO

iMX6

SD2_DAT2

SD2_DATA2

SD2_DATA2

ALT0 / ALT0

V_VIO_S0

S29 SDMMC_D3

Bi-Dir

-

CMOS / VDD_IO

iMX6

SD2_DAT3

SD2_DATA3

SD2_DATA3

ALT0 / ALT0

V_VIO_S0

S30 SDMMC_D4

Bi-Dir

PU-1k

CMOS / VDD_IO

iMX6

NANDF_D4 SD2_DATA4

SD2_DATA4

ALT1 / ALT1

V_1V8_S0

S31 SDMMC_D5

Bi-Dir

PU-1k

CMOS / VDD_IO

iMX6

NANDF_D5 SD2_DATA5

SD2_DATA5

ALT1 / ALT1

V_1V8_S0

S32 SDMMC_D6

Bi-Dir

PU-1k

CMOS / VDD_IO

iMX6

NANDF_D6 SD2_DATA6

SD2_DATA6

ALT1 / ALT1

V_1V8_S0

S33 SDMMC_D7

Bi-Dir

PU-1k

CMOS / VDD_IO

iMX6

NANDF_D7 SD2_DATA7

SD2_DATA7

ALT1 / ALT1

V_1V8_S0

S34 GND

-

-

-

-

-

-

-

-

-

S35 SDMMC_CK

Out

-

CMOS / VDD_IO

iMX6

SD2_CLK

SD2_CLK

SD2_CLK

ALT0 / ALT0

V_VIO_S0

S36 SDMMC_CMD

Bi-Dir

PU-10k

CMOS / VDD_IO

iMX6

SD2_CMD

SD2_CMD

SD2_CMD

ALT0 / ALT0

V_VIO_S0

S37

SDMMC_RST#

Out

-

CMOS / VDD_IO

CPLD

-

-

-

-

V_VIO_S5

S38

AUDIO_MCK

Out

-

CMOS / VDD_IO

iMX6

NANDF_CS

2

CCM_CLKO2

CCM_CLKO2

ALT4 / ALT4

V_VIO_S0

S39

I2S0_LRCK

Bi-Dir

-

CMOS / VDD_IO

iMX6

CSI0_DAT6 AUD3_TXFS

AUD3_TXFS

ALT4 / ALT4

V_VIO_S0

S40

I2S0_SDOUT

Out

-

CMOS / VDD_IO

iMX6

CSI0_DAT5 AUD3_TXD

AUD3_TXD

ALT4 / ALT4

V_VIO_S0

S41

I2S0_SDIN

In

-

CMOS / VDD_IO

iMX6

CSI0_DAT7 AUD3_RXD

AUD3_RXD

ALT4 / ALT4

V_VIO_S0

S42

I2S0_CK

Bi-Dir

-

CMOS / VDD_IO

iMX6

CSI0_DAT4 AUD3_TXC

AUD3_TXC

ALT4 / ALT4

V_VIO_S0

S43

I2S1_LRCK

Bi-Dir

-

CMOS / VDD_IO

iMX6

DISP0_DAT

22

AUD4_TXFS

AUD4_TXFS

ALT3 / ALT3

V_VIO_S0

S44

I2S1_SDOUT

Out

-

CMOS / VDD_IO

iMX6

DISP0_DAT

21

AUD4_TXD

AUD4_TXD

ALT3 / ALT3

V_VIO_S0

S45

I2S1_SDDIN

In

-

CMOS / VDD_IO

iMX6

DISP0_DAT

23

AUD4_RXD

AUD4_RXD

ALT3 / ALT3

V_VIO_S0

S46

I2S1_CK

Bi-Dir

-

CMOS / VDD_IO

iMX6

DISP0_DAT

20

AUD4_TXC

AUD4_TXC

ALT3 / ALT3

V_VIO_S0

26