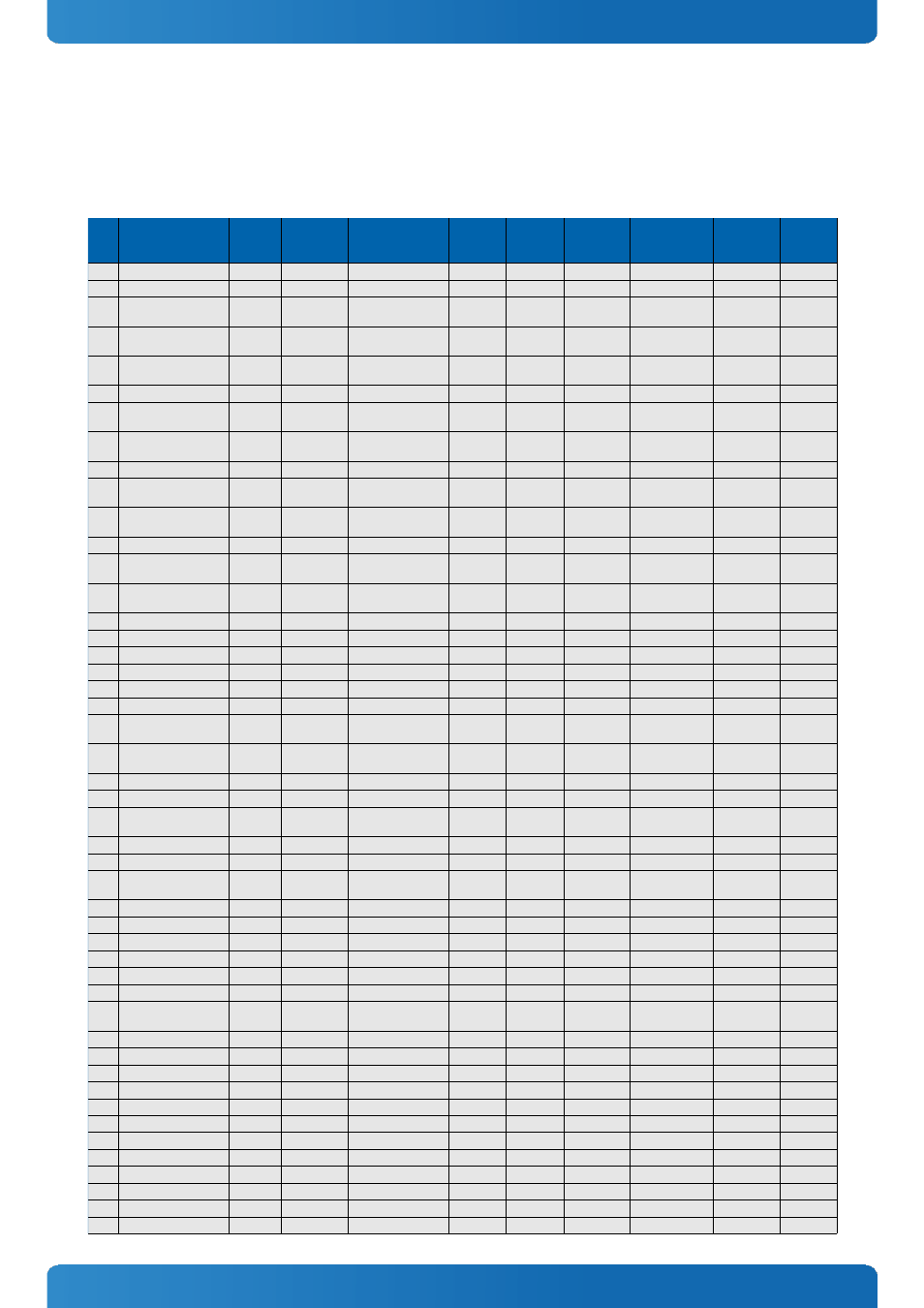

4 connectors, 1 smarc™ connector top side, Connectors – Kontron SMARC-sAMX6i User Manual

Page 22: Smarc™ connector top side, Smarc-samx6i / connectors

SMARC-sAMX6i / Connectors

4 Connectors

The pinouts for Interface Connector are documented for convenient reference. Please see the SMARC Specification and

SMARC Design Guide for detailed, design-level information.

4.1

SMARC™ Connector Top Side

Pin

Signal

Module

Direction

Module

Termination

Type/Tolerance

Controller Controller

Pin Name

Port(i.MX6

Quad/Dual)

Port(i.MX6

Solo)

I/O MUX

Instance

Quad/Solo

Power Rail

P1

PCAM_PXL_CK1

In

-

CMOS / VDD_IO

-

-

N.C.

N.C.

-

-

P2

GND

-

-

-

-

-

-

-

-

-

P3

CSI1_CK+ / PCAM_D0

In

-

LVDS D-PHY / VDD_IO iMX6

EIM_A17

IPU2_CSI1_

DATA12

GPIO2_IO21 (*1) ALT2 / ALT5

V_VIO_S0

P4

CSI1_CK- / PCAM_D1

In

-

LVDS D-PHY / VDD_IO iMX6

EIM_A18

IPU2_CSI1_

DATA13

GPIO2_IO20 (*1) ALT2 / ALT5

V_VIO_S0

P5

PCAM_DE

In

-

CMOS / VDD_IO

iMX6

EIM_D23

IPU2_CSI1_

DATA_EN

GPIO3_IO23 (*1) ALT2 / ALT5

V_VIO_S0

P6

PCAM_MCK

Out

-

CMOS / VDD_IO

iMX6

GPIO_3

CCM_CLKO2

CCM_CLKO2

ALT4 / ALT4

V_VIO_S0

P7

CSI1_D0+ / PCAM_D2

In

-

LVDS D-PHY / VDD_IO iMX6

EIM_A19

IPU2_CSI1_

DATA14

GPIO2_IO19 (*1) ALT2 / ALT5

V_VIO_S0

P8

CSI1_D0- / PCAM_D3

In

-

LVDS D-PHY / VDD_IO iMX6

EIM_A20

IPU2_CSI1_

DATA15

GPIO2_IO18 (*1) ALT2 / ALT5

V_VIO_S0

P9

GND

-

-

-

-

-

-

-

-

-

P10

CSI1_D1+ / PCAM_D4

In

-

LVDS D-PHY / VDD_IO iMX6

EIM_A21

IPU2_CSI1_

DATA16

GPIO2_IO17 (*1) ALT2 / ALT5

V_VIO_S0

P11

CSI1_D1- / PCAM_D5

In

-

LVDS D-PHY / VDD_IO iMX6

EIM_A22

IPU2_CSI1_

DATA17

GPIO2_IO16 (*1) ALT2 / ALT5

V_VIO_S0

P12

GND

-

-

-

-

-

-

-

-

-

P13

CSI1_D2+ / PCAM_D6

In

-

LVDS D-PHY / VDD_IO iMX6

EIM_A23

IPU2_CSI1_

DATA18

GPIO6_IO06 (*1) ALT2 / ALT5

V_VIO_S0

P14

CSI1_D2- / PCAM_D7

In

-

LVDS D-PHY / VDD_IO iMX6

EIM_A24

IPU2_CSI1_

DATA19

GPIO5_IO04 (*1) ALT2 / ALT5

V_VIO_S0

P15

GND

-

-

-

-

-

-

-

-

-

P16

CSI1_D3+ / PCAM_D8

IN

-

LVDS D-PHY / VDD_IO -

-

N.C.

N.C.

-

-

P17

CSI1_D3- / PCAM_D9

IN

-

LVDS D-PHY / VDD_IO -

-

N.C.

N.C.

-

-

P18

GND

-

-

-

-

-

-

-

-

-

P19

GBE_MDI3-

Bi-Dir

-

GBE MDI

BCM54610

TRD3M

RGMII

RGMII

-

-

P20

GBE_MDI3+

Bi-Dir

-

GBE MDI

BCM54610

TRD3P

RGMII

RGMII

-

-

P21

GBE_LINK100#

Out / OD

-

VDD_IO

BCM54610

/ CPLD

-

RGMII

RGMII

-

-

P22

GBE_LINK1000#

Out / OD

-

VDD_IO

BCM54610

/ CPLD

-

RGMII

RGMII

-

-

P23

GBE_MDI2-

Bi-Dir

-

GBE MDI

BCM54610

TRD2M

RGMII

RGMII

-

-

P24

GBE_MDI2+

Bi-Dir

-

GBE MDI

BCM54610

TRD2P

RGMII

RGMII

-

-

P25

GBE_LINK_ACT#

Out / OD

-

VDD_IO

BCM54610

/ CPLD

-

RGMII

RGMII

-

-

P26

GBE_MDI1-

Bi-Dir

-

GBE MDI

BCM54610

TRD1M

RGMII

RGMII

-

-

P27

GBE_MDI1+

Bi-Dir

-

GBE MDI

BCM54610

TRD1P

RGMII

RGMII

-

-

P28

GBE_CTREF

Out

-

V-Ref

100nF to

GND

-

RGMII

RGMII

-

-

P29

GBE_MDI0-

Bi-Dir

-

GBE MDI

BCM54610

TRD0M

RGMII

RGMII

-

-

P30

GBE_MDI0+

Bi-Dir

-

GBE MDI

BCM54610

TRD0P

RGMII

RGMII

-

-

P31

SPI0_CS1#

Out

-

CMOS / VDD_IO

iMX6

EIM_D25

ECSPI4_SS3

-

ALT1 / ALT1

V_VIO_S0

P32

GND

-

-

-

-

-

-

-

-

-

P33

SDIO_WP

In

W-PU

CMOS 3.3V

iMX6

ENET_RXD1 GPIO1_IO26

GPIO1_IO26

ALT5 / ALT5

V_3V3_S0

P34

SDIO_CMD

Bi-Dir

PU-10k

CMOS 3.3V

iMX6

SD3_CMD

SD3_CMD

SD3_CMD

ALT0 / ALT0

V_3V3_S0

P35

SDIO_CD#

In

PU-10k

CMOS 3.3V

iMX6

NANDF_CS

1

GPIO6_IO14

GPIO6_IO14

ALT5 / ALT5

V_1V8_S0

P36

SDIO_CK

Out

-

CMOS 3.3V

iMX6

SD3_CLK

SD3_CLK

SD3_CLK

ALT0 / ALT0

V_3V3_S0

P37

SDIO_PWR_EN

Out

-

CMOS 3.3V

iMX6

ENET_TXD1 GPIO1_IO29

GPIO1_IO29

ALT5 / ALT5

V_3V3_S0

P38

GND

-

-

-

-

-

-

-

-

-

P39

SDIO_D0

Bi-Dir

-

CMOS 3.3V

iMX6

SD3_DAT0

SD3_DATA0

SD3_DATA0

ALT0 / ALT0

V_3V3_S0

P40

SDIO_D1

Bi-Dir

-

CMOS 3.3V

iMX6

SD3_DAT1

SD3_DATA1

SD3_DATA1

ALT0 / ALT0

V_3V3_S0

P41

SDIO_D2

Bi-Dir

-

CMOS 3.3V

iMX6

SD3_DAT2

SD3_DATA2

SD3_DATA2

ALT0 / ALT0

V_3V3_S0

P42

SDIO_D3

Bi-Dir

PD-300k

CMOS 3.3V

iMX6

SD3_DAT3

SD3_DATA3

SD3_DATA3

ALT0 / ALT0

V_3V3_S0

P43

SPI0_CS0#

Out

-

CMOS / VDD_IO

CPLD

-

-

-

-

V_VIO_S5

-

-

-

-

-

iMX6

EIM_D29

ECSPI4_SS0

ECSPI4_SS0

ALT2 / ALT2

V_VIO_S0

-

-

-

-

-

iMX6

EIM_D24

ECSPI4_SS2

ECSPI4_SS2

ALT1 / ALT1

V_VIO_S0

P44

SPI0_CK

Out

Serial 20R

CMOS / VDD_IO

iMX6

EIM_D21

ECSPI4_SCLK ECSPI4_SCLK

ALT1 / ALT1

V_VIO_S0

P45

SPI0_DIN

In

Serial 0R

CMOS / VDD_IO

iMX6

EIM_D22

ECSPI4_MIS

ECSPI4_MISO

ALT1 / ALT1

V_VIO_S0

22