Come-msp1 / system resources – Kontron COMe-mSP1 User Manual

Page 55

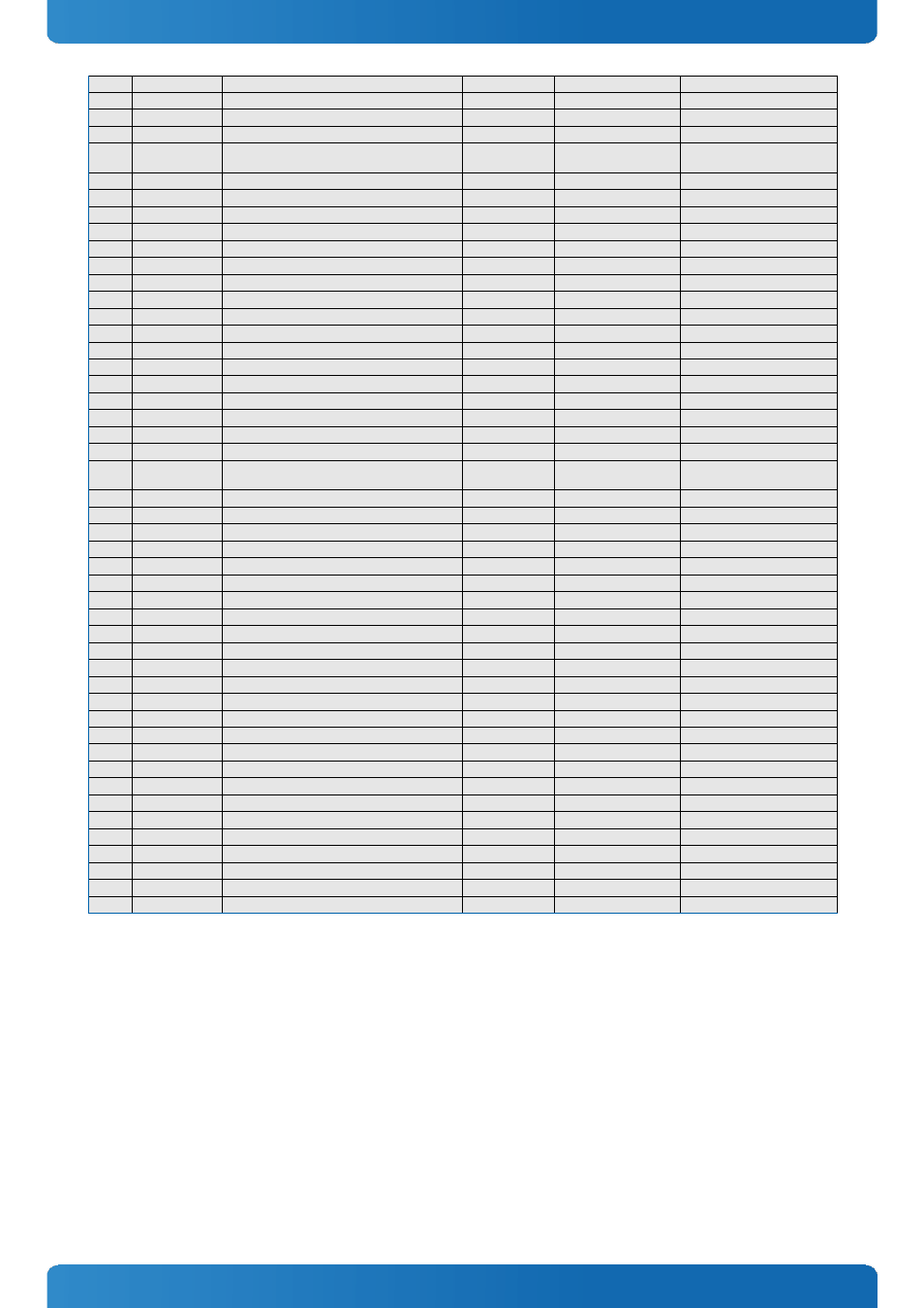

COMe-mSP1 / System Resources

3.3V

A64

PCIE_TX1+

PCIe lane #1 Transmit+

DP-O

PU 50R inUS15W

only available on no-LAN var.

A65

PCIE_TX1-

PCIe lane #1 Transmit-

DP-O

PU 50R inUS15W

only available on no-LAN var.

A66

GND_9

Power Ground

PWR

-

-

A67

SDIO_D2 / GPI2

SDIO#0 Data2 / General Purpose Input 2

I/O-3.3 / I-3.3

PU 75k in US15W / PU 100k

3.3V

- / CPLD I/O

A68

PCIE_TX0+

PCIe lane #0 Transmit+

DP-O

PU 50R inUS15W

-

A69

PCIE_TX0-

PCIe lane #0 Transmit-

DP-O

PU 50R inUS15W

-

A70

GND_10

Power Ground

PWR

-

-

A71

LVDS_A0+

LVDS Channel A (positive)

DP-O

PU 50R inUS15W

-

A72

LVDS_A0-

LVDS Channel A (negative)

DP-O

PU 50R inUS15W

-

A73

LVDS_A1+

LVDS Channel A (positive)

DP-O

PU 50R inUS15W

-

A74

LVDS_A1-

LVDS Channel A (negative)

DP-O

PU 50R inUS15W

-

A75

LVDS_A2+

LVDS Channel A (positive)

DP-O

PU 50R inUS15W

-

A76

LVDS_A2-

LVDS Channel A (negative)

DP-O

PU 50R inUS15W

-

A77

LVDS_VDD_EN

LVDS Panel Power Control

O-3.3

PD 100k

-

A78

LVDS_A3+

LVDS Channel A (positive)

DP-O

PU 50R inUS15W

-

A79

LVDS_A3-

LVDS Channel A (negative)

DP-O

PU 50R inUS15W

-

A80

GND_11

Power Ground

PWR

-

-

A81

LVDS_A_CK+

LVDS Channel A Clock+

DP-O

PU 50R inUS15W

-

A82

LVDS_A_CK-

LVDS Channel A Clock-

DP-O

PU 50R inUS15W

-

A83

LVDS_I2C_CK

LVDS I2C Clock (DDC)

IO-3.3

PU 10k 3.3V

-

A84

LVDS_I2C_DAT

LVDS I2C Data (DDC)

IO-3.3

PU 10k 3.3V

-

A85

SDIO_D3 / GPI3

SDIO# Data3 / General Purpose Input 3

I/O-3.3 / I-3.3

PU 75k in US15W / PU 100k

3.3V

- / CPLD I/O

A86

KBD_RST#

Keyboard Reset

I-5T

PU 1M 3.3V

not supported on CE 1.x.x

A87

KBD_A20GATE

A20 gate

I-5T

PU 10k 3.3V

-

A88

PCIE0_CK_REF+

PCIe Clock (positive)

DP-O

-

100MHz

A89

PCIE0_CK_REF-

PCIe Clock (negative)

DP-O

-

100MHz

A90

GND_12

Power Ground

PWR

-

-

A91

RSVD1

Reserved

nc

-

-

A92

RSVD2

Reserved

nc

-

-

A93

SDIO_Clk / GPO0

SDIO#0 Clock / General Purpose Output 0

O-3.3 / O-3.3

- / PD 100k

24/48MHz / CPLD I/O

A94

RSVD3

Reserved

nc

-

-

A95

RSVD4

Reserved

nc

-

-

A96

GND_13

Power Ground

PWR

-

-

A97

VCC_12V_1

12V VCC

PWR

-

-

A98

VCC_12V_2

12V VCC

PWR

-

-

A99

VCC_12V_3

12V VCC

PWR

-

-

A100

GND_14

Power Ground

PWR

-

-

A101

VCC_12V_4

12V VCC

PWR

-

-

A102

VCC_12V_5

12V VCC

PWR

-

-

A103

VCC_12V_6

12V VCC

PWR

-

-

A104

VCC_12V_7

12V VCC

PWR

-

-

A105

VCC_12V_8

12V VCC

PWR

-

-

A106

VCC_12V_9

12V VCC

PWR

-

-

A107

VCC_12V_10

12V VCC

PWR

-

-

A108

VCC_12V_11

12V VCC

PWR

-

-

A109

VCC_12V_12

12V VCC

PWR

-

-

A110

GND_15

Power Ground

PWR

-

-

55