Pin definitions – Cypress CY7C1394BV18 User Manual

Page 6

CY7C1392BV18, CY7C1992BV18

CY7C1393BV18, CY7C1394BV18

Document #: 38-05623 Rev. *D

Page 6 of 31

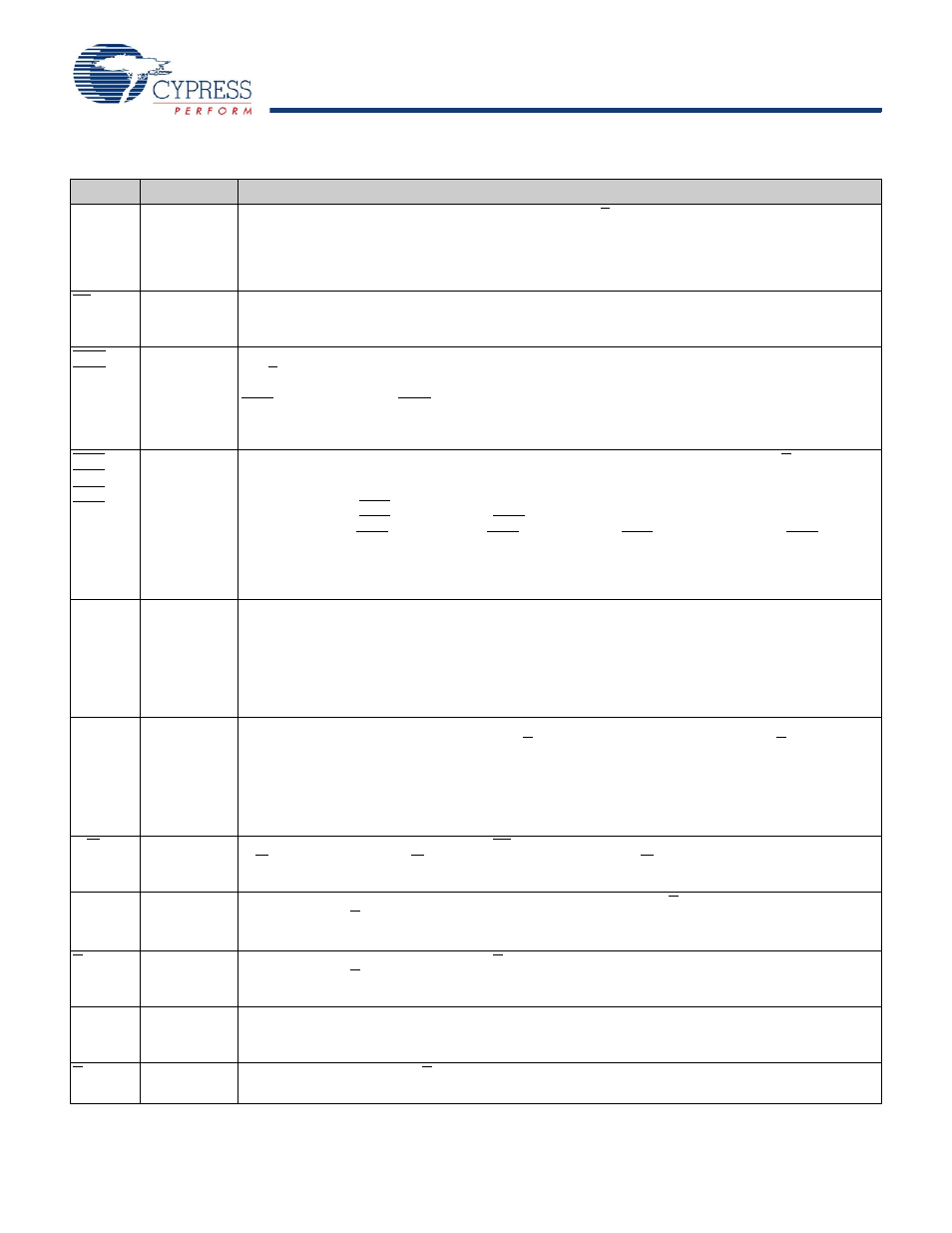

Pin Definitions

Pin Name

IO

Pin Description

D

[x:0]

Input-

Synchronous

Data Input Signals. Sampled on the rising edge of K and K clocks during valid write operations.

CY7C1392BV18 - D

[7:0]

CY7C1992BV18 - D

[8:0]

CY7C1393BV18 - D

[17:0]

CY7C1394BV18 - D

[35:0]

LD

Input-

Synchronous

Synchronous Load. This input is brought LOW when a bus cycle sequence is defined. This definition

includes address and read/write direction. All transactions operate on a burst of 2 data (one clock period

of bus activity).

NWS

0

,

NWS

1

Nibble Write Select 0, 1

− Active LOW (CY7C1392BV18 Only). Sampled on the rising edge of the K

and K clocks during Write operations. Used to select which nibble is written into the device during the

current portion of the Write operations.Nibbles not written remain unaltered.

NWS

0

controls D

[3:0]

and NWS

1

controls D

[7:4]

.

All Nibble Write Selects are sampled on the same edge as the data. Deselecting a Nibble Write Select

ignores the corresponding nibble of data and it is not written into the device.

BWS

0

,

BWS

1

,

BWS

2

,

BWS

3

Input-

Synchronous

Byte Write Select 0, 1, 2 and 3

− Active LOW. Sampled on the rising edge of the K and K clocks during

write operations. Used to select which byte is written into the device during the current portion of the write

operations. Bytes not written remain unaltered.

CY7C1992BV18

− BWS

0

controls D

[8:0]

CY7C1393BV18

− BWS

0

controls D

[8:0]

, BWS

1

controls D

[17:9]

.

CY7C1394BV18

− BWS

0

controls D

[8:0]

, BWS

1

controls D

[17:9]

,BWS

2

controls D

[26:18]

and BWS

3

controls

D

[35:27].

All the Byte Write Selects are sampled on the same edge as the data. Deselecting a Byte Write Select

ignores the corresponding byte of data and it is not written into the device.

A

Input-

Synchronous

Address Inputs. Sampled on the rising edge of the K clock during active read and write operations. These

address inputs are multiplexed for both read and write operations. Internally, the device is organized as

2M x 8 (2 arrays each of 1M x 8) for CY7C1392BV18, 2M x 9 (2 arrays each of 1M x 9) for CY7C1992BV18,

1M x 18 (2 arrays each of 512K x 18) for CY7C1393BV18 and 512K x 36 (2 arrays each of 256K x 36)

for CY7C1394BV18. Therefore, only 20 address inputs are needed to access the entire memory array of

CY7C1392BV18 and CY7C1992BV18, 19 address inputs for CY7C1393BV18 and 18 address inputs for

CY7C1394BV18. These inputs are ignored when the appropriate port is deselected.

Q

[x:0]

Outputs-

Synchronous

Data Output Signals. These pins drive out the requested data during a read operation. Valid data is

driven out on the rising edge of both the C and C clocks during read operations, or K and K when in single

clock mode. When the read port is deselected, Q

[x:0]

are automatically tri-stated.

CY7C1392BV18

− Q

[7:0]

CY7C1992BV18

− Q

[8:0]

CY7C1393BV18

− Q

[17:0]

CY7C1394BV18

− Q

[35:0]

R/W

Input-

Synchronous

Synchronous Read/Write Input. When LD is LOW, this input designates the access type (read when

R/W is HIGH, write when R/W is LOW) for the loaded address. R/W must meet the setup and hold times

around the edge of K.

C

Input Clock

Positive Input Clock for Output Data. C is used in conjunction with C to clock out the read data from

the device. C and C can be used together to deskew the flight times of various devices on the board back

to the controller. See

on page 9 for further details.

C

Input Clock

Negative Input Clock for Output Data. C is used in conjunction with C to clock out the read data from

the device. C and C can be used together to deskew the flight times of various devices on the board back

to the controller. See

on page 9 for further details.

K

Input Clock

Positive Input Clock Input. The rising edge of K is used to capture synchronous inputs to the device

and to drive out data through Q

[x:0]

when in single clock mode. All accesses are initiated on the rising

edge of K.

K

Input Clock

Negative Input Clock Input. K is used to capture synchronous inputs being presented to the device and

to drive out data through Q

[x:0]

when in single clock mode.