Noise considerations, Preventing autostore, Stk14d88 – Cypress Perform STK14D88 User Manual

Page 13

STK14D88

Document Number: 001-52037 Rev. **

Page 13 of 17

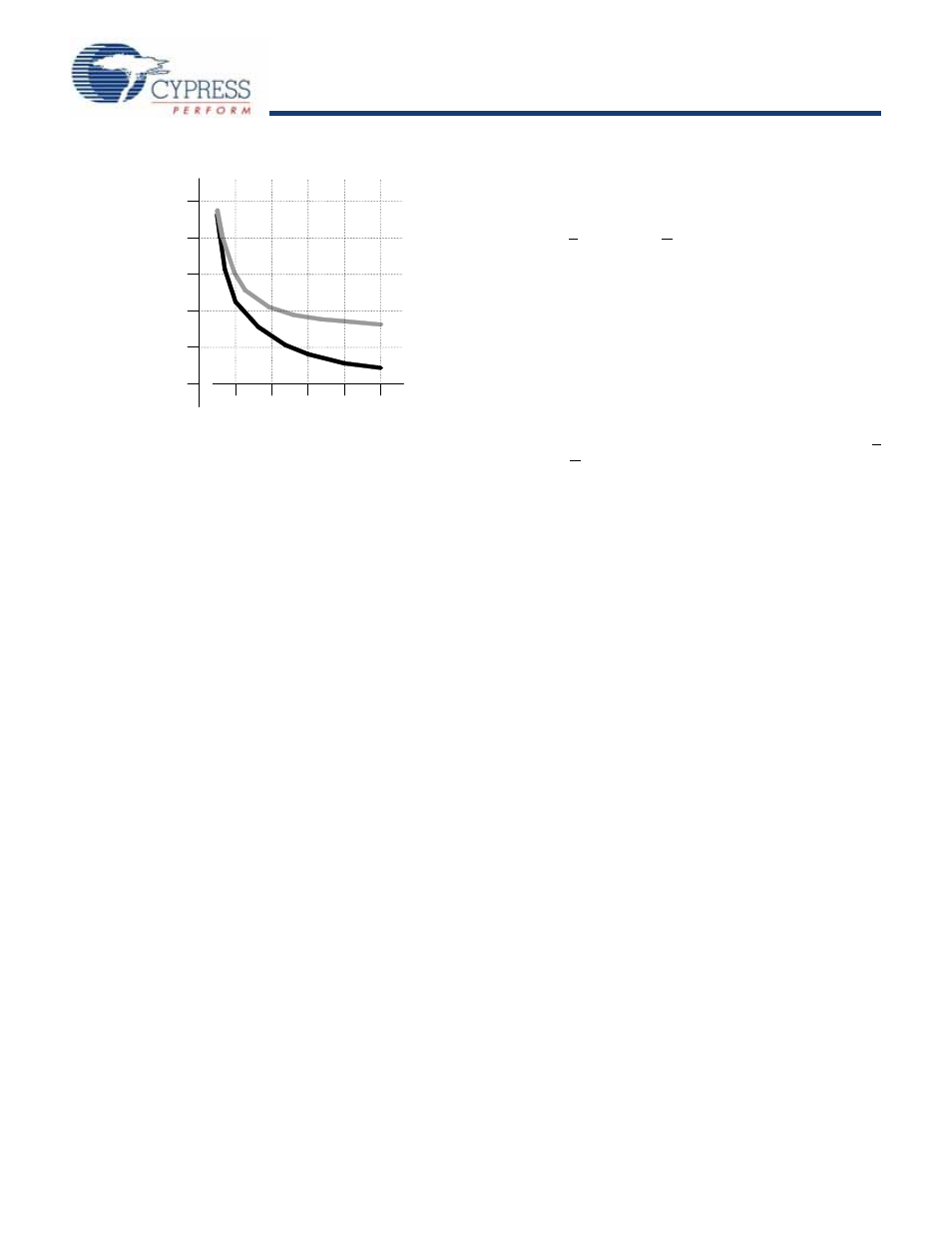

Figure 13. Current versus Cycle Time

Noise Considerations

The STK14D88 is a high-speed memory and so must have a

high-frequency bypass capacitor of 0.1 µF connected between

both V

CC

pins and V

SS

ground plane with no plane break to chip

V

SS

. Use leads and traces that are as short as possible. As with

all high-speed CMOS ICs, careful routing of power, ground, and

signals will reduce circuit noise.

Preventing AutoStore

The AutoStore function can be disabled by initiating an

AutoStore Disable sequence. A sequence of READ operations

is performed in a manner similar to the software STORE initi-

ation. To initiate the AutoStore Disable sequence, the following

sequence of E controlled or G controlled READ operations must

be performed:

1. Read Address 0x0E38, Valid READ

2. Read Address 0x31C7, Valid READ

3. Read Address 0x03E0, Valid READ

4. Read Address 0x3C1F, Valid READ

5. Read Address 0x303F, Valid READ

6. Read Address 0x03F8, AutoStore Disable

The AutoStore can be re-enabled by initiating an AutoStore

Enable sequence. A sequence of READ operations is performed

in a manner similar to the software RECALL initiation. To initiate

the AutoStore Enable sequence, the following sequence of E

controlled or G controlled READ operations must be performed:

1. Read Address 0x0E38, Valid READ

2. Read Address 0x31C7, Valid READ

3. Read Address 0x03E0, Valid READ

4. Read Address 0x3C1F, Valid READ

5. Read Address 0x303F, Valid READ

6. Read Address 0x07F0, AutoStore Enable

If the AutoStore function is disabled or re-enabled, a manual

STORE operation (Hardware or Software) needs to be issued to

save the AutoStore state through subsequent power down

cycles. The part comes from the factory with AutoStore enabled.

In all cases, make sure the READ sequence is uninterrupted. For

example, an interrupt that occurs in the sequence that reads the

nvSRAM would abort this sequence, resulting in an error.

A

v

er

age

Act

iv

e

C

u

rrent

(mA)

100 150 200 300

0

10

20

30

40

50

Writes

Reads

Cycle Time (ns)

50