Vicor PFC Micro Power Factor Corrected AC-DC Switcher User Manual

Page 13

PFC Micro Design Guide

General Shutdown /GSD (CBJ3-10)

The GSD control pin on CBJ3-10 allows simultaneous shutdown of all outputs. This pin must be pulled down to

less than 0.7V, and will typically source 250

μA (1mA maximum) to shut down all outputs. The GSD pin should be

open circuited or driven high to a logic high voltage of 3.5V or greater when not in use, or when the outputs are to

be enabled. Do not apply more than 5V to this input.

AC OK (CBJ3-3)

AC OK is an active high TTL compatible signal and provides a status indication of the AC input power. It is on pin

CBJ3-3 and is capable of sinking 5 mA maximum. This signal switches to a TTL "1" when the high voltage bus

exceeds low-line condition during turn-on. Upon loss of input power, the bus voltage will drop, causing the AC OK

signal to go low. Typically, a 3 ms holdup time is provided for a 500W load following the loss of the AC OK sig-

nal.

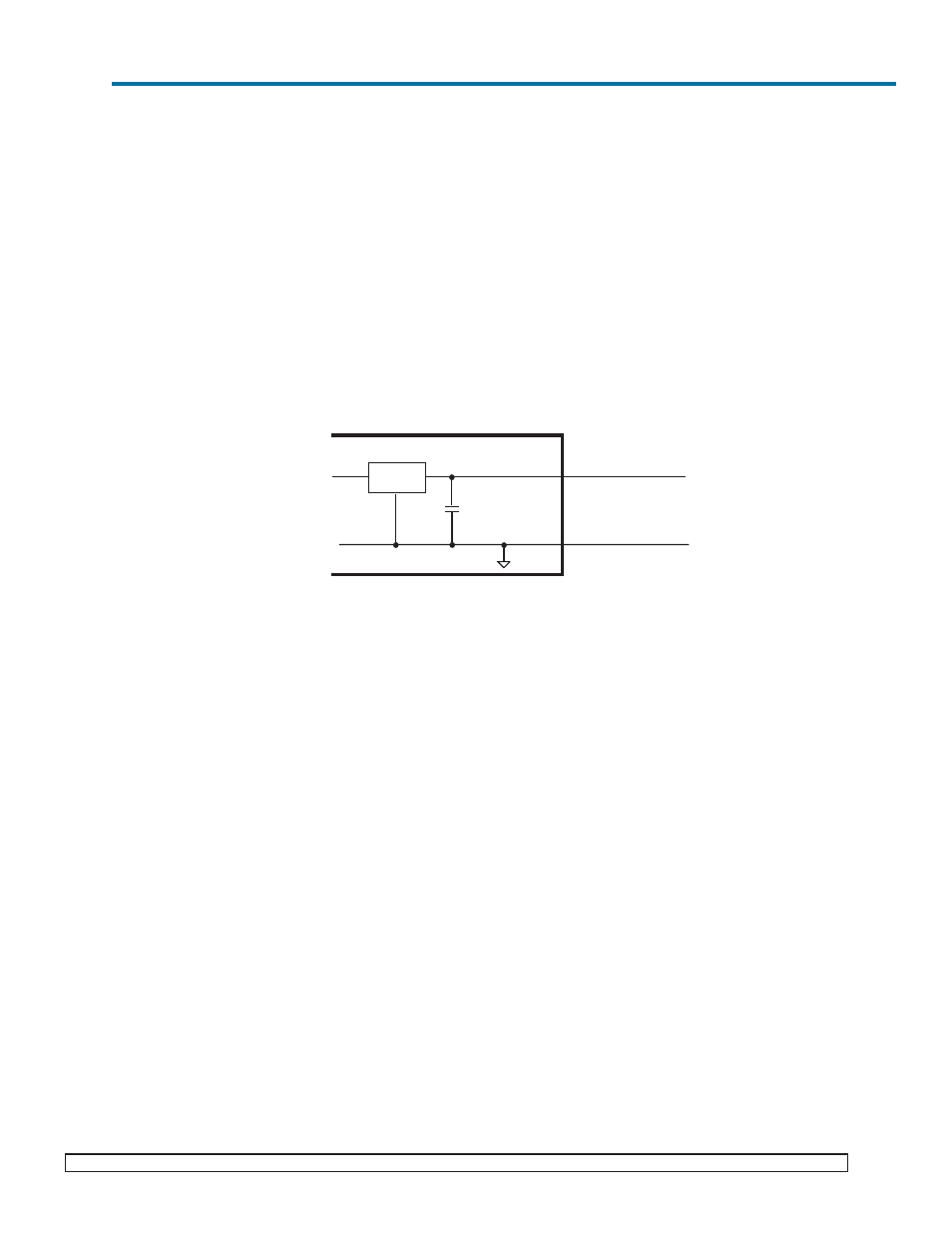

Auxiliary Vcc +5V/40mA (CBJ3-12)

The Vcc on CBJ3-12 is an auxiliary 5V regulated power source. It is +5 Vdc +/–5% with respect to Signal Ground

and can supply 40 mA maximum. It is capable of withstanding a short, but shorted user interface functionality will

be lost.

Power Good Read (PGR, CBJ3-2)

This pin initiates the Power Good Read sequence. A logic high applied to this pin will cause the power supply to

enter the Power Good Read status mode. In this mode, the I/O lines (CBJ3-4 to CBJ3-9) will be outputs. These

outputs give an indication of the status of the modules of the power supply. A high on an I/O line (CBJ3-4 to

CBJ3-9) indicates a module is ON and functioning and a low indicate the module is OFF or in a fault condition.

The Power Good Status data will be valid on the ED lines (CBJ3-4 to CBJ3-9) when the Power Good Data Valid

(PGDV) pin (CBJ3-11) asserts a logic high. Applying a logic low or opening the PGR pin puts the power supply

back in the Enable/Disable mode. Instructions for using this function are on page 11 under Module Power Good

Status Mode

Power Good Data Valid (PGDV- CBJ3-11)

Upon entering the Power Good Read status mode (PGR=1, CBJ3-2), the data will not be valid on the I/O lines

(CBJ3-4 to CBJ3-9) until the PGDV pin asserts itself logic high. This pin can source up to 5mA. When this pin is

logic low, Power Good status data is not valid or the power supply is not in the Power Good Read status mode.

+Sense/ –Sense (S1/S2 J2)

The sense lines for the outputs are shipped from the factory with Autosense. Autosense provides the user with

automatic sensing of the outputs. With Autosense, the PFC Micro will automatically operate in a Remote Sense

mode when the Remote Sense connections are made. But in the event that the Remote Sense is not connected or

needed, no Local Sense selection is necessary - simply hook up the outputs and the PFC Micro will automatically

operate in Local Sense mode.

In the local sense mode (Remote Sense lines not connected), the power supply will regulate the output at the output

terminals. The voltage appearing at the load may drop slightly due to voltage drop in the power cables. If it is nec-

essary to compensate for voltage drop along the output power cables, the output can be trimmed up or configured

for Remote Sense. Use stranded twisted pair 20-22 AWG wire for the Remote Sense lines. Remote Sense can com-

pensate for a voltage drop of up to 0.5V, or 0.25V on each leg.

78M05

Auxiliary Vcc

CBJ3-12

0.1 µF

Signal Ground

CBJ3

CBJ3-1

+5V/40 mA

Figure 4. Auxiliary Vcc

03-000048 rev A

Vicor 800-735-6200 Westcor Division 408-522-5280 Applications Engineering 800-927-9474 Pg. 13