BNC 6040 User Manual

Page 54

54

THEORY OF OPERATION

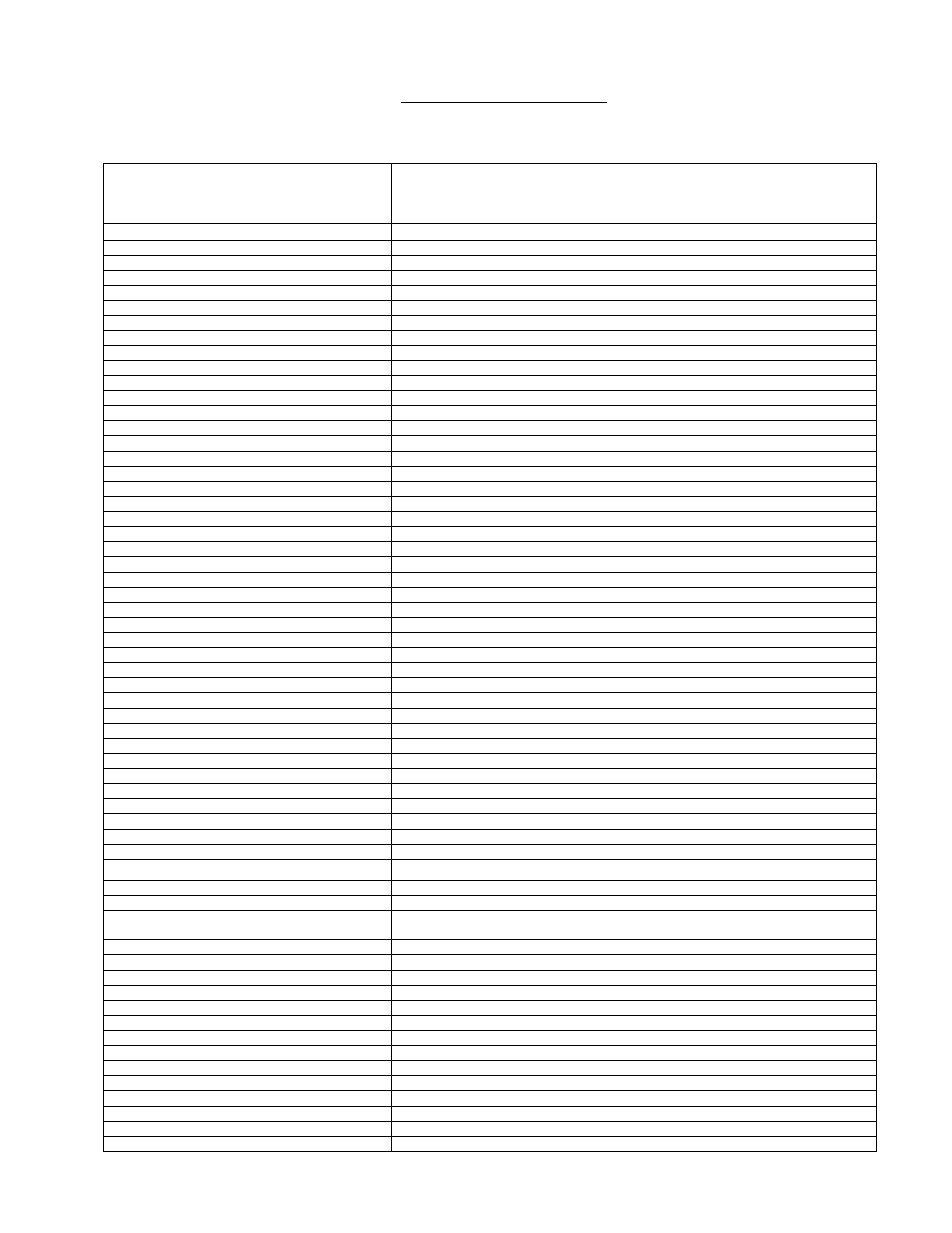

Table 1-10. Mainframe Memory Map

Memory Range

Description

CODE:

0000 – FFFF

64K EPROM, Z17, 27C512

DATA I/O

0000 – 1FFF

8K RAM, Z24, 6264

C000 – DFFF

Plug-In Module (see module manual)

E800 – EFFF

Memory Mapped I/O

E800 – E8FF

Z16, 82C54; DELAY

E800

LSW Counter

E801

MSW Counter

E802

Prescaler

E803

Control Register

E900 – E9FF

Z20, 82C54, WIDTH

E900

LSW Counter

E901

MSW Counter

E902

Prescaler

E903

Control Register

EA00 – EAFF

Z23, 82C54, PLL1

EA00

Divides PLLIN to produce PLLVA

EA02

Divides FTTL1 to produce FTTL2

EA03

Control Register

EB00 – EBFF

Z27, 82C54; PLL2, RATE LIMIT

EB00

Divides Crystal to 500.0 Hz PLLREF

EB01

Outputs RLMTHD

EB02

Unused

EB03

Control Register

EC00 – ECFF

Z33, 82C55; FRONT PANEL CONTROL

EC00

Port A, Keypad column scan output

EC01

Port B, LCD and LED data BUS

EC02

Port C, Keypad row scan input

EC03

Control Register

ED00 – EDFF

Z22, 82C55; ECL TRIGGER CONTROL

ED00

Port A, Trigger Control

ED01

Port B, External Trigger DAC

ED02

Port C, Error Input, CMOS Enable

ED03

Control Register

EE00 – EEFF

Z19, 82C55; ECL TIMING CONTROL

EE00

Port A, Delay 1 and 10 ns

EE01

Port B, Width 1 and 10 ns

EE02

Port C, Load Timing

EE03

Control Register

EF00 – EFFF

Z4, TMS9914; IEEE-488 INTERFACE

EF00

Interrupt 0 status/mask

EF01

Interrupt 1 status/mask

EF02

Address Status

EF03

Bus Status / Auxiliary Command

EF04

Address

EF05

Serial Poll

EF06

Command Pass Through / Parallel Poll

EF07

Data In/Out