Lock-out period delays, 1 rationale behind the lock-out period delays, Table 1. wakeup delays – Cirrus Logic AN186 User Manual

Page 6: To wakeup operations, An186

AN186

6

AN186REV1

5. LOCK-OUT PERIOD DELAYS

These delays can be described as the amount of delay from when the WAKEUP signal first rises, until the CPU starts fetching

instructions. There are two cases of these wakeup delays in the EP72/73XX. One case is the cold boot that can happen after

power-up, in changing a battery, or a power failure. The second instance occurs after software has forced the device into the

Standby State. In both cases, the internal system clock is turned off to save power consumption. To resume the normal operation

upon receiving the WAKEUP signal, the system has to wait until the system clock is stabilized. This waiting period is defined

as the Lock-out Period.

The internal system clock is controlled by an internally generated signal (Internal RUN), which is activated by the wakeup

source with a predefined delay time (lock-out period delay). This delay will ensure the clock source is stabilized before the

internal system clock is turned on. When the internal system clock starts running, the device resumes the normal operation in

which instructions are executed.

5.1 Rationale behind the Lock-out Period Delays

The amount of the lock-out period delay has been hardwired internally to ensure that enough time has elapsed for the clock

source to be stable before the clock to the CPU is enabled. It also varies depending upon the source of system clock (external

oscillator or internal PLL). In a system that is designed to use the internal PLL or the oscillator with an enable / disable feature,

it takes some time (a few hundred ms) to establish a stable clock output after powering on the PLL or the external oscillator.

Therefore, the internal system clock enable signal (Internal RUN) should wait a longer time than in the case when the oscillator

is always running. The specific wakeup delays are tabulated in Table 1.

6. THE FUNCTION OF "RUN/CLKEN" OUTPUT PIN AS IT RELATES TO WAKEUP

OPERATIONS

There is a multipurpose output pin named “RUN/CLKEN”. The function of the pin is determined by one bit (CLKENSL) in the

SYSCON2 register. When CLKENSL = 0, it configures this pin to become the “CLKEN” signal. When CLKENSL = 1, it

configures it to become the “RUN” signal. Both signals are affected by the WAKEUP signal and play an important role in the

wakeup operation. Their relationship will be described below.

Regardless of the origin of the clock source (the external OSC or PLL), when the RUN/CLKEN is programmed as “RUN,” the

Internal RUN signal is brought out through this pin, which can be used as an indicator of the internal state of the device. In this

case, the wakeup delay is directly measurable through the RUN signal, and the variance of the delay amount can be observed

in different configurations.

When the RUN/CLKEN pin is programmed as “CLKEN,” it is designed to enable or disable the external oscillator under the

control of the EP72/73XX. Since it is desirable to promptly turn “on” the oscillator upon receiving the WAKEUP signal, the

time delay from the WAKEUP signal to the CLKEN activation (0 to 1) is designed to be minimal (almost immediate). It takes

between 62 - 125 us to deglitch the WAKEUP input. Immediately after the WAKEUP signal is deglitched, CLKEN will go high.

Then CLKEN can be used to re-enable the external oscillator. CLKEN can be used as an indicator of the internal state of the

EP72/73XX, but is not recommended because there is a latency period (CLKEN to Internal RUN) involved until the wakeup

delay lapses. In this case, the wakeup delay is not directly measurable, but can be observed indirectly by monitoring activities

on other functional pins such as a GPIO pin.

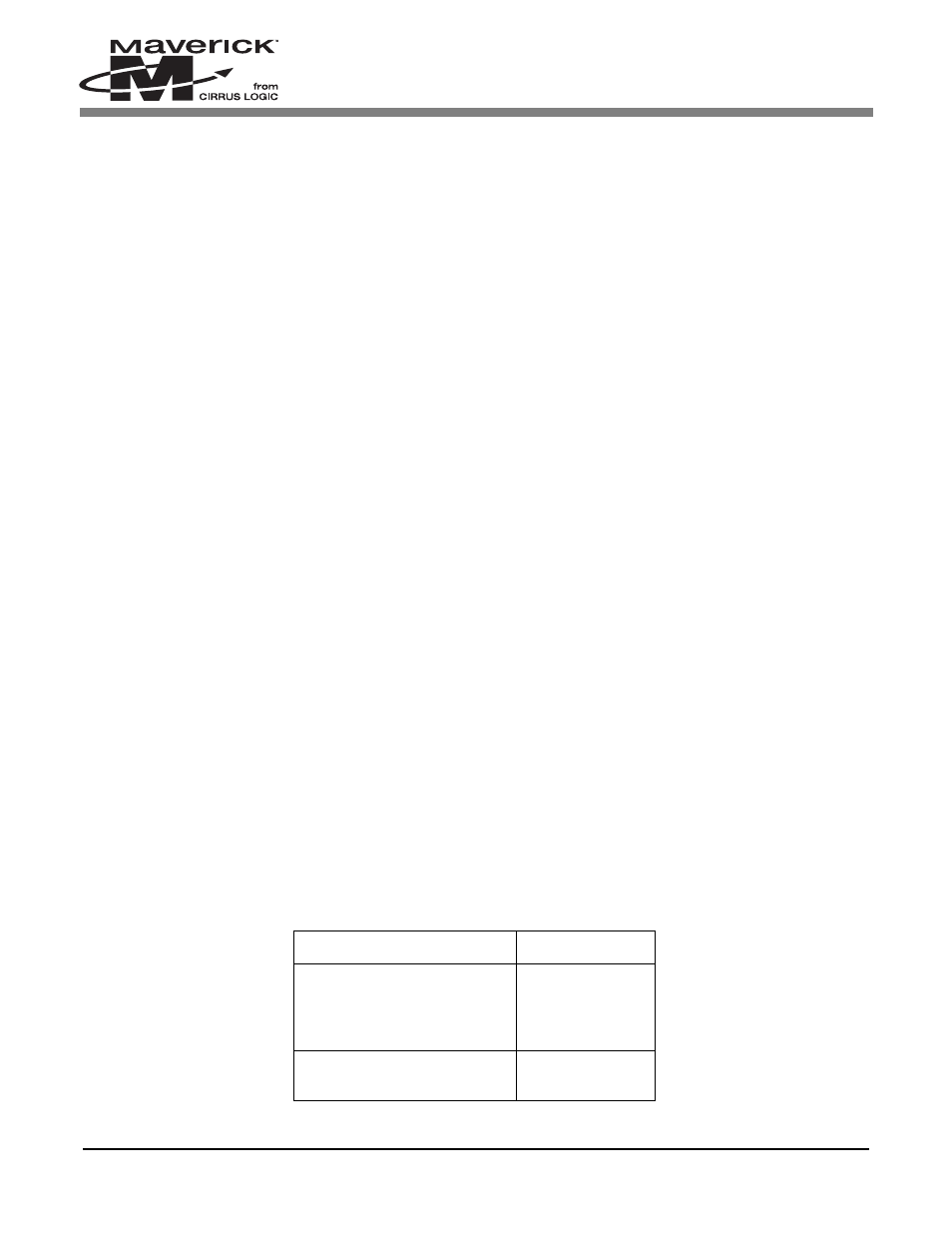

Case

Wakeup Delay

Cold boot

PLL

External Oscillator with

enable

125 - 250ms

External Oscillator when

always “on”

62 - 125us(mini-

mum)

Table 1. Wakeup Delays