2 voltage reference input, Cdb5451a – Cirrus Logic CDB5451A User Manual

Page 7

CDB5451A

DS458DB3

7

differential signal. Using voltage channel #1 as an

example (see Figure 2), note that HDR10 sets the

input to the positive side of the first voltage channel

input (VIN1+ pin). HDR13 sets the input to the

negative side of the first voltage channel input

(VIN1- pin). In a single-ended input configuration,

HDR13 would be set to the “AGND” setting, and

HDR10 would be set to “VIN1+” and would conduct

the single-ended signal. In a differential input con-

figuration, HDR13 would be set to “VIN1-” and

HDR10 would be set to “VIN1+” and this pair of in-

puts would form the differential input pair into the

VIN1+ and VIN1- pins of the CS5451A.

WARNING: DANGER! One of the possible appli-

cations for the CS5451A includes data acquisition

for a power metering system. However, the user

should not attempt to directly connect any lead

from a high-voltage power line to the evaluation

board inputs, even if the current/voltage levels are

gain reduced by resistive dividers and/or shunts.

Because the ground terminal of the parallel cable

(from the PC) is near or at earth ground potential,

the ground node on the evaluation board will also

be forced to earth ground potential. Serious dam-

age and even personal injury can occur if a “hot”

voltage main is connected to any point on the eval-

uation board, including the analog input connec-

tors. Such power line signals must be isolated by

current/voltage transformers and reduced in mag-

nitude before they can be safely applied to the

evaluation board.

Several patch-circuit areas are provided near the

voltage/current input headers, in case the user

wants to connect special sensor circuitry to the an-

alog inputs (such as transformers, shunt resistors,

etc., for monitoring a 3-phase power line). For

each of the three channels, a Shunt Resistor or

Current Transformer can be mounted in these ar-

eas and connections can be made to the individual

current-channel input pairs. Likewise, for each of

the three voltage channels, a Voltage Divider or

Voltage Transformer can be inserted to drive the

CS5451A’s three voltage input pairs. Note from

Figure 2 that a simple R-C network filters each

sensor’s output to reduce any noise that might be

coupled into the input leads. The 3 dB corner of the

filter is approximately 50 kHz differential and com-

mon mode.

Other header options listed in Table 2 allow the

user to set the source of the input clock signal and

the source of the voltage reference (VREFIN) in-

put, etc. The voltage reference options and clock

input options are discussed next.

2.3.2 Voltage Reference Input

To supply the CS5451A with a suitable 1.2 V volt-

age reference input at the VREFIN pin, the evalu-

ation board provides three voltage reference

options: on-chip, on-board, and external. See

HDR14 as shown in Figure 1. Table 3 illustrates

the available voltage reference settings for

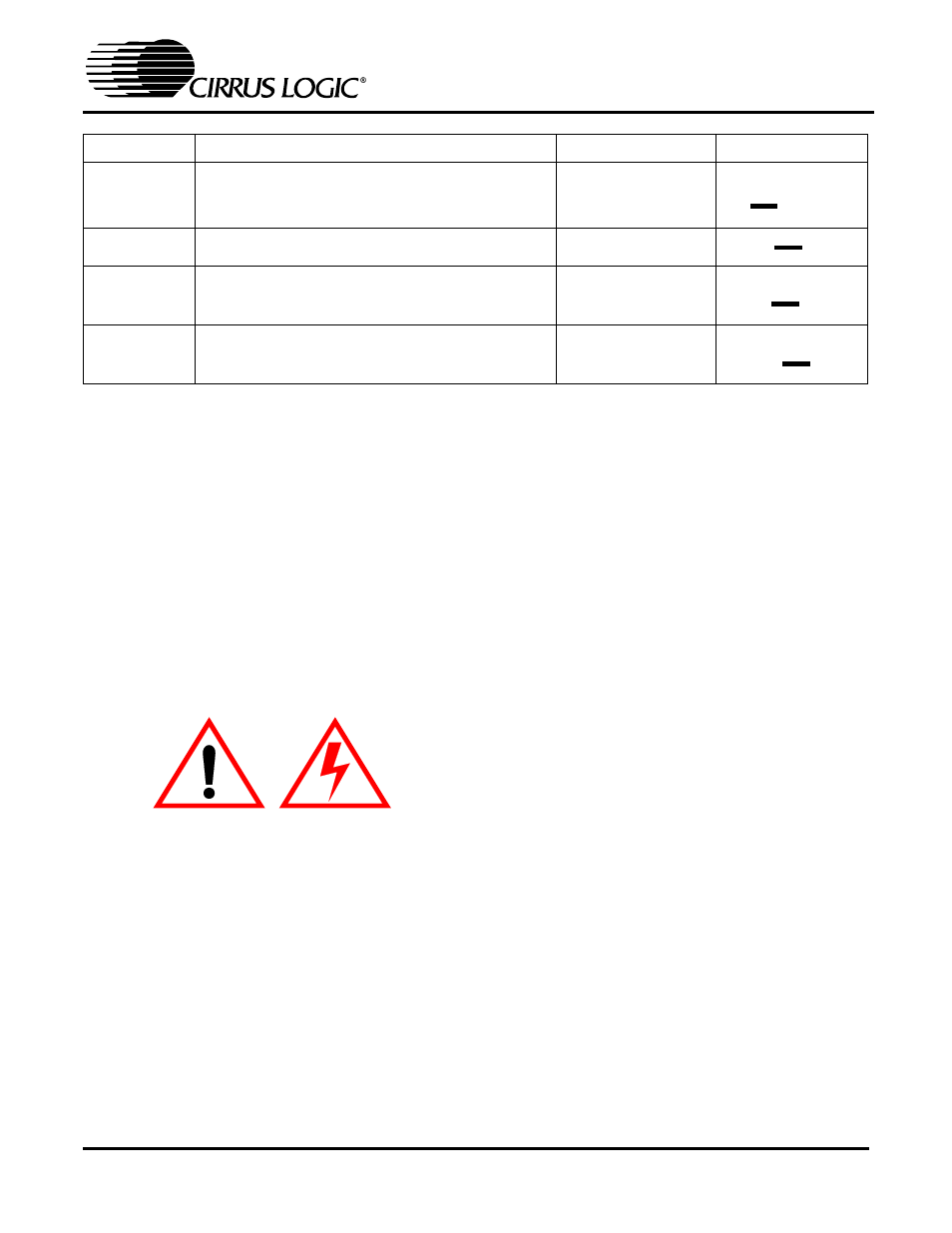

HDR14. With HDR14’s jumpers in position “VRE-

HDR15

Controls the source for the CS5451A XIN clock

input.

Set to on-board 4.000

MHz crystal (U1).

HDR16

This header should always be shorted.

Short this header

HDR17

Determines whether the main analog supply will be

powered from the A- post, or from the regulated 3V

voltage (generated from the +5V_IN) post input.

Set to A-

HDR18

Choose whether the digital circuitry will be powered

by main analog supply, or powered by separate dig-

ital supply (through VD+ post).

Set to main analog

supply

Name

Function Description

Default Setting

Default Jumpers

Table 2. Default Header Settings (Continued)

O O EXT XIN

O O DGND

O O 4.0096 MHz

OSC

O O

O O +5V_IN

O O A+

O O

O O

VD+

V+