2 master mode, Figure 23. cs5361 master mode clocking, Table 3. cs5361 common master clock frequencies – Cirrus Logic CS5361 User Manual

Page 17: Cs5361

CS5361

DS467F2

17

4.2.2

Master Mode

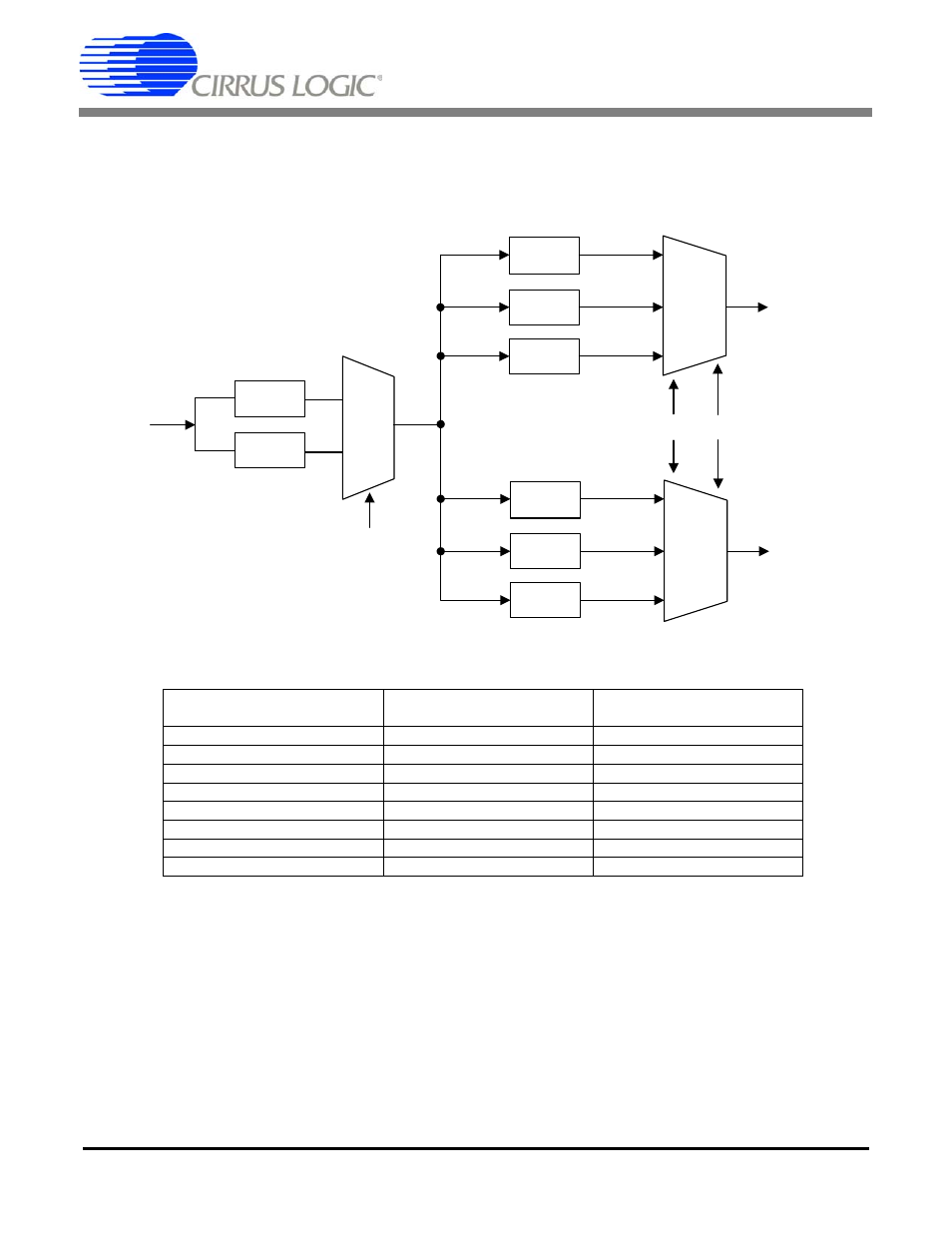

In Master mode, LRCK and SCLK operate as outputs. The left/right and serial clocks are internally derived from the

master clock with the left/right clock equal to Fs and the serial clock equal to 64x Fs, as shown in Figure 23. Refer

to Table 3 for common master clock frequencies.

ч 128

ч 256

ч 64

M0

M1

LRCK Output

(Equal to Fs)

Single

Speed

Quad

Speed

Double

Speed

00

01

10

ч 2

ч 4

ч 1

SCLK Output

Single

Speed

Quad

Speed

Double

Speed

00

01

10

ч 2

ч 1

0

1

MCLK

MDIV

Figure 23. CS5361 Master Mode Clocking

SAMPLE RATE (kHz)

MDIV = 0

MCLK (MHz)

MDIV = 1

MCLK (MHz)

32

8.192

16.384

44.1

11.2896

22.5792

48

12.288

24.576

64

8.192

16.384

88.2

11.2896

22.5792

96

12.288

24.576

176.4

11.2896

22.5792

192

12.288

24.576

Table 3. CS5361 Common Master Clock Frequencies

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)