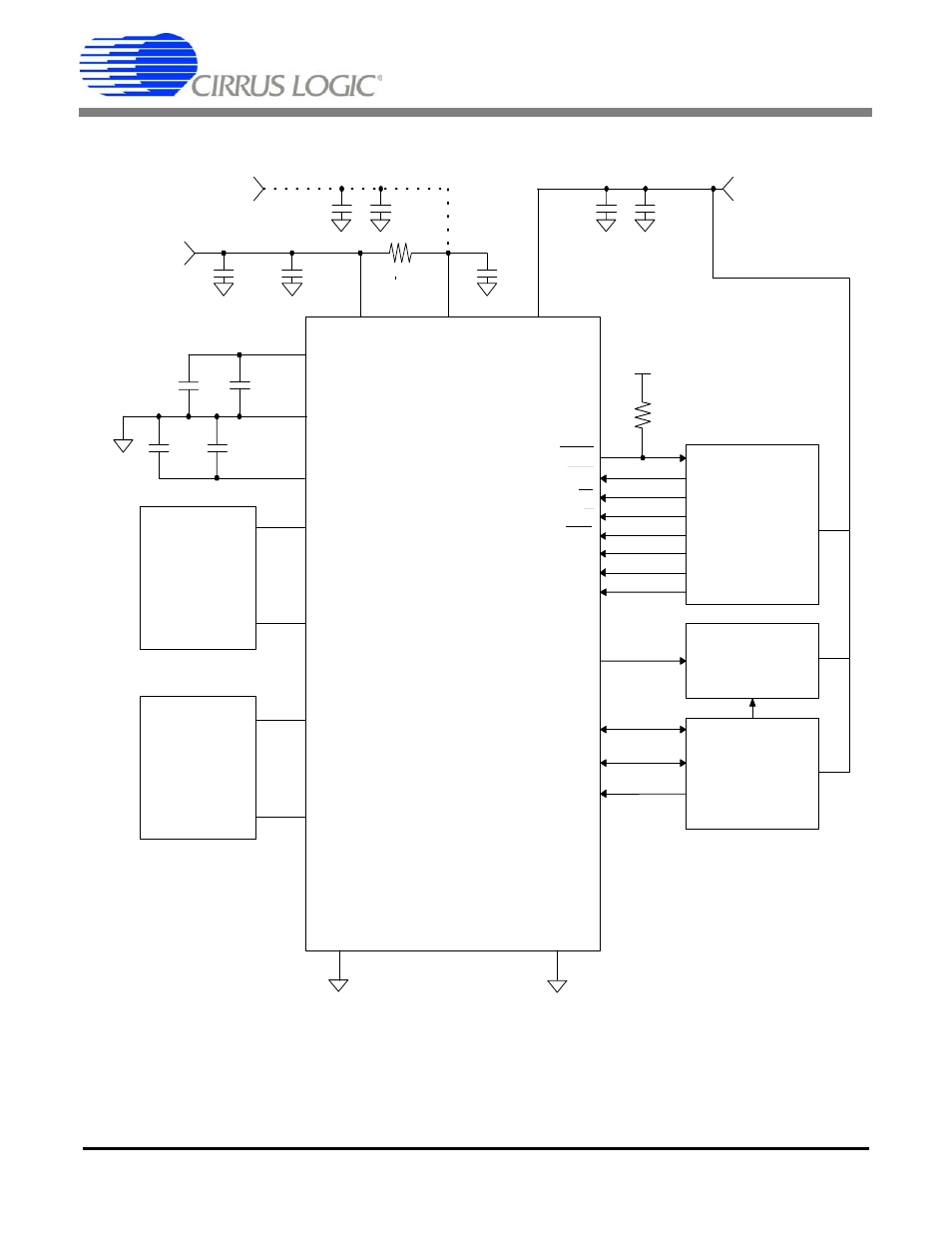

0 typical connection diagram, Figure 22. typical connection diagram, Cs5361 – Cirrus Logic CS5361 User Manual

Page 15

CS5361

DS467F2

15

FILT+

AINL+

AINL-

V

D

0.01

µF

A/D CONVERTER

SCLK

CS5361

M/S

MCLK

AINR+

AINR-

VQ

**47

µF

+

RST

VA

V

L

+5V

1

µF

+5Vto 2.5 V

5.1

Ω

1

µF

+

+

+

SDOUT

GND

I

2

S/LJ

LRCK

GND

Power Down

and Mode

Settings

Audio Data

Processor

Timing Logic

and Clock

0.01

µF

0.01

µF

0.01

µF

HPF

M0

M1

REFGND

MDIV

+5 V to 3.3 V

1

µF

0.01

µF

1

µF

+

Analog

Input

Buffer

(Figure 24)

Analog

Input

Buffer

(Figure 24)

OVFL

10 k

VL

*

0.01

µF

* Resistor may only

be used if VD is

derived from VA. If

used, do not drive any

other logic from VD.

3.0 TYPICAL CONNECTION DIAGRAM

Figure 22. Typical Connection Diagram

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)