2 analog input selection (bits 2:0), Table 13. analog input multiplexer selection, 9 active level control - address 0ch – Cirrus Logic CS5345 User Manual

Page 36: 1 active high/low (bit 0), 10 interrupt status - address 0dh, Interrupt, Table 12, Cs5345

36

DS658F4

CS5345

6.8.2

Analog Input Selection (Bits 2:0)

Function:

These bits are used to select the input source for the PGA and ADC. Please see

.

6.9

Active Level Control - Address 0Ch

6.9.1

Active High/Low (Bit 0)

Function:

When this bit is set, the INT pin functions as an active high CMOS driver.

When this bit is cleared, the INT pin functions as an active low open drain driver and will require an exter-

nal pull-up resistor for proper operation.

6.10

Interrupt Status - Address 0Dh

For all bits in this register, a ‘1’ means the associated interrupt condition has occurred at least once since

the register was last read. A ‘0’ means the associated interrupt condition has NOT occurred since the last

reading of the register. Status bits that are masked off in the associated mask register will always be ‘0’ in

this register. This register defaults to 00h.

PGASoft

PGAZeroCross

Mode

0

0

Changes to affect immediately

0

1

Zero Cross enabled

1

0

Soft Ramp enabled

1

1

Soft Ramp and Zero Cross enabled (default)

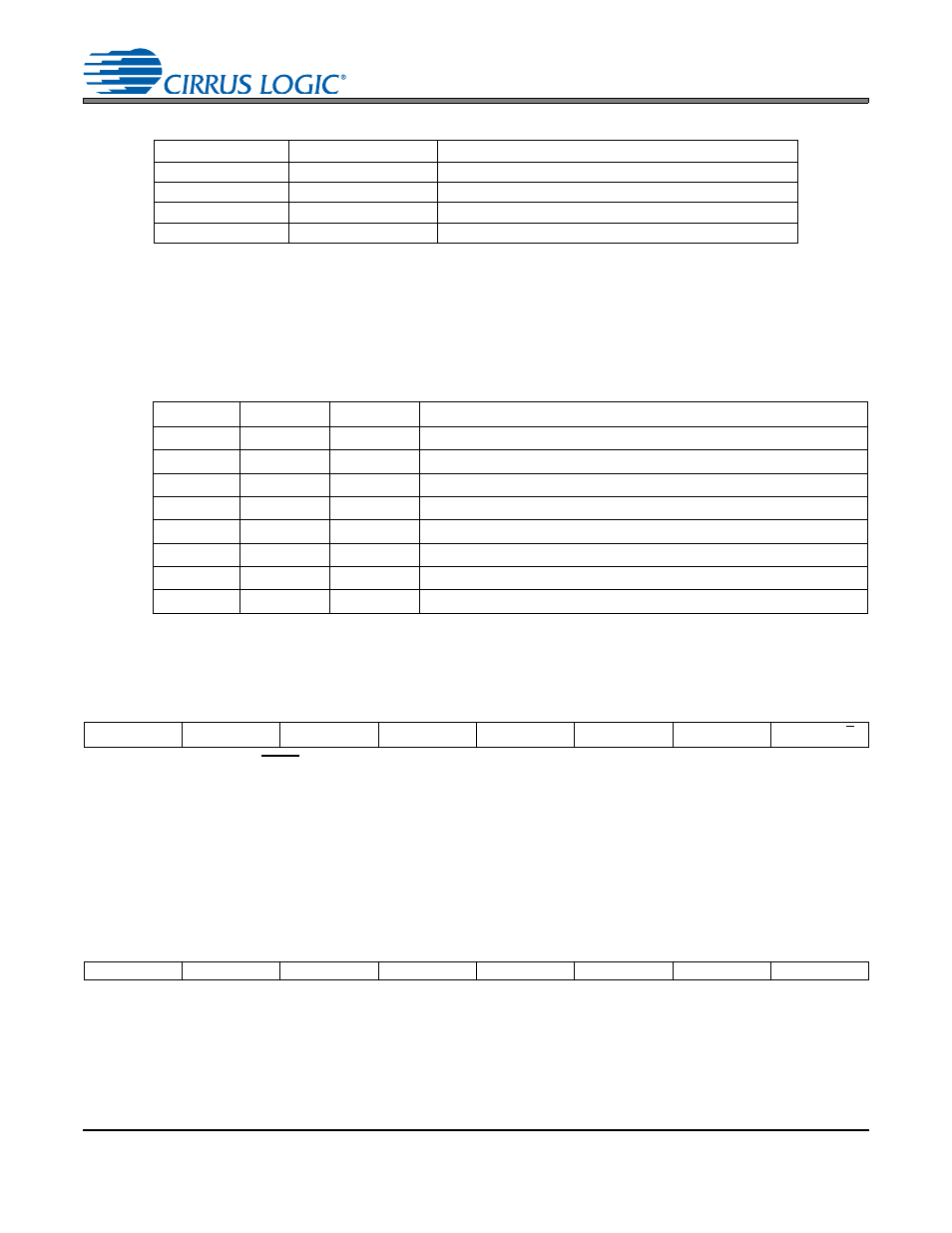

Table 12. PGA Soft Cross or Zero Cross Mode Selection

Sel2

Sel1

Sel0

PGA/ADC Input

0

0

0

Microphone-Level Inputs (+32 dB Gain Enabled)

0

0

1

Line-Level Input Pair 1

0

1

0

Line-Level Input Pair 2

0

1

1

Line-Level Input Pair 3

1

0

0

Line-Level Input Pair 4

1

0

1

Line-Level Input Pair 5

1

1

0

Line-Level Input Pair 6

1

1

1

Reserved

Table 13. Analog Input Multiplexer Selection

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Active_H/L

7

6

5

4

3

2

1

0

Reserved

Reserved

Reserved

Reserved

ClkErr

Reserved

Ovfl

Undrfl