1 operation as a clock master, Figure 18. cs5341 master mode clocking, 2 operation as a clock slave with auto-detect – Cirrus Logic CS5341 User Manual

Page 16: Figure 18.cs5341 master mode clocking

16

DS564F2

CS5341

Confidential Draft

3/11/08

4.2.1

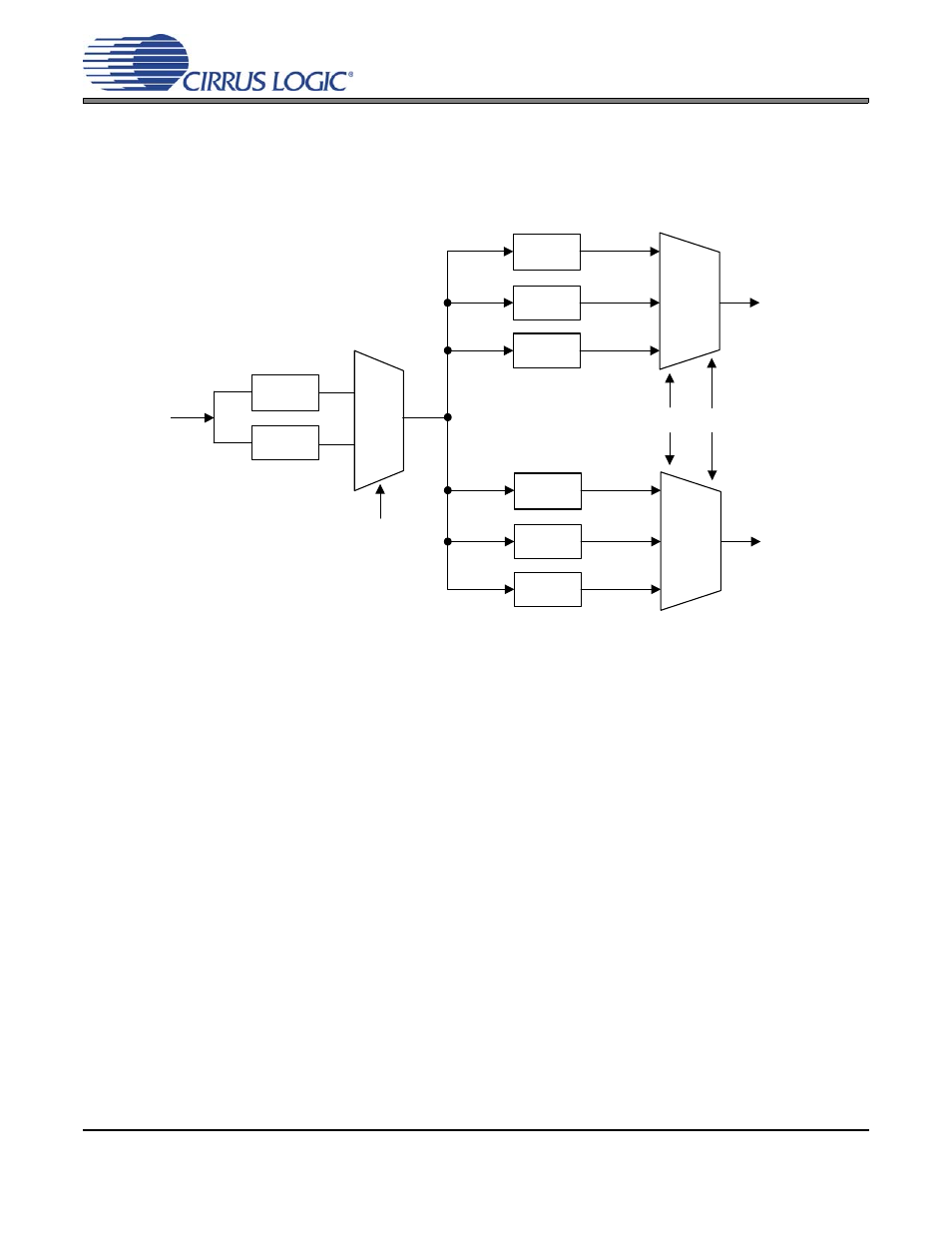

Operation as a Clock Master

As a clock master, LRCK and SCLK operate as outputs. The left/right and serial clocks are internally de-

rived from the master clock with the left/right clock equal to Fs and the serial clock equal to 64x Fs, as

shown in

4.2.2

Operation as a Clock Slave with Auto-Detect

LRCK and SCLK operate as inputs in clock Slave Mode. It is recommended that the left/right clock be

synchronously derived from the master clock and must be equal to Fs. It is also recommended that the

serial clock be synchronously derived from the master clock and be equal to 64x Fs to maximize system

performance.

A unique feature of the CS5341 is the automatic selection of either Single-, Double- or Quad-Speed Mode

when operating as a clock slave. The auto-mode select feature negates the need to configure the Mode

pins to correspond to the desired mode. The auto-mode selection feature supports all standard audio

sample rates from 2 to 200 kHz. However, there are ranges of non-standard audio sample rates that are

not supported when operating with a fast MCLK (512x, 256x, 128x for Single-, Double-, and Quad-Speed

Modes, respectively). Please refer to

for supported sample rate ranges.

ч 128

ч 256

ч 64

M0

M1

LRCK Output

(Equal to Fs)

Single

Speed

Quad

Speed

Double

Speed

00

01

10

ч 2

ч 4

ч 1

SCLK Output

Single

Speed

Quad

Speed

Double

Speed

00

01

10

ч 2

ч 1

0

1

MCLK

Auto-Select

Figure 18. CS5341 Master Mode Clocking