Busy/ i2c_select clk/scl miso/sda int – Cirrus Logic CS48LV13 User Manual

Page 19

19

DS1057F1

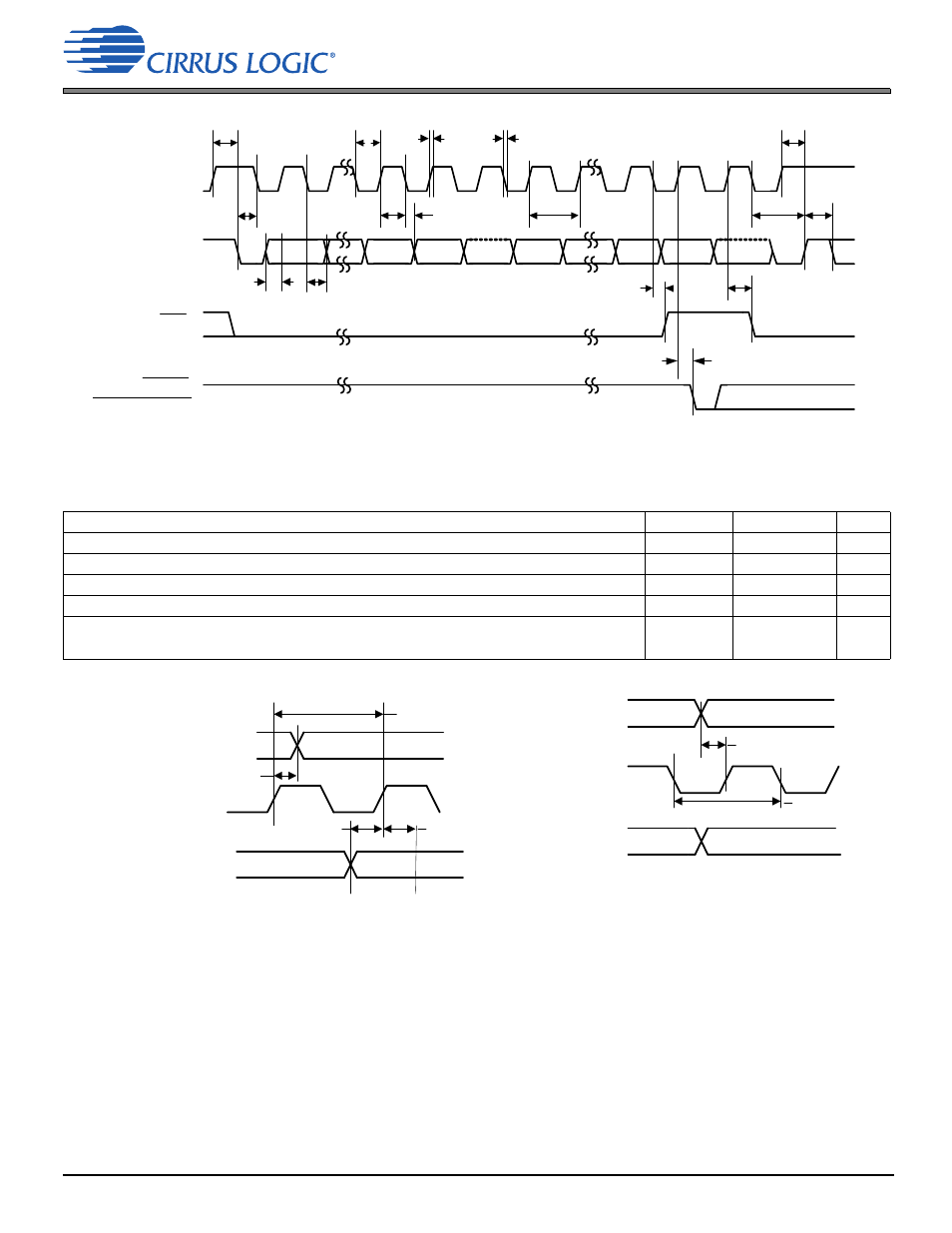

4.12 Switching Characteristics—Digital Audio Slave Input Port

Figure 4-6. Serial Control Port—I

2

C Slave Mode Timing

4.12 Switching Characteristics—Digital Audio Slave Input Port

Figure 4-7. DAI Port Slave Timing Diagram

Parameter

Symbol

Min

Max

Unit

SCLK period

T

daiclkp

40

—

ns

SCLK duty cycle

—

45

55

%

Setup time DAI_Dx

1

1.All DAI data lines are timed relative to active edge of SCLK

t

daidsu

10

—

ns

Hold time DAI_Dx

t

daidh

5

—

ns

Slave mode

SCLK active edge to LRCLK transition

t

daisstlr

10

—

ns

LRCLK transition to SCLK active edge

t

daislrts

10

—

ns

BUSY/

I2C_SELECT

CLK/SCL

MISO/SDA

INT

0

1

6

7

8

0

1

7

t

iicckl

t

iicckh

t

iicsu

t

iich

A6

A0

R/W

ACK

LSB

t

iicirqh

t

iicirql

8

ACK

MSB

t

iicstp

6

t

iiccbsyl

t

hddo

t

iicbft

t

iicstscl

t

iicckcmd

f

iicck

t

iicckcmd

t

iicf

t

iicr

DAI_SCLK

DAI_LRCLK

DAI_Dx

t

daislrts

t

daiclkp

DAI_SCLK

DAI_LRCLK

t

daisstlr

t

daidh

t

daiclkp

DAI_Dx

t

daidsu