Cirrus Logic CS48LV13 User Manual

Page 14

DS1057F1

14

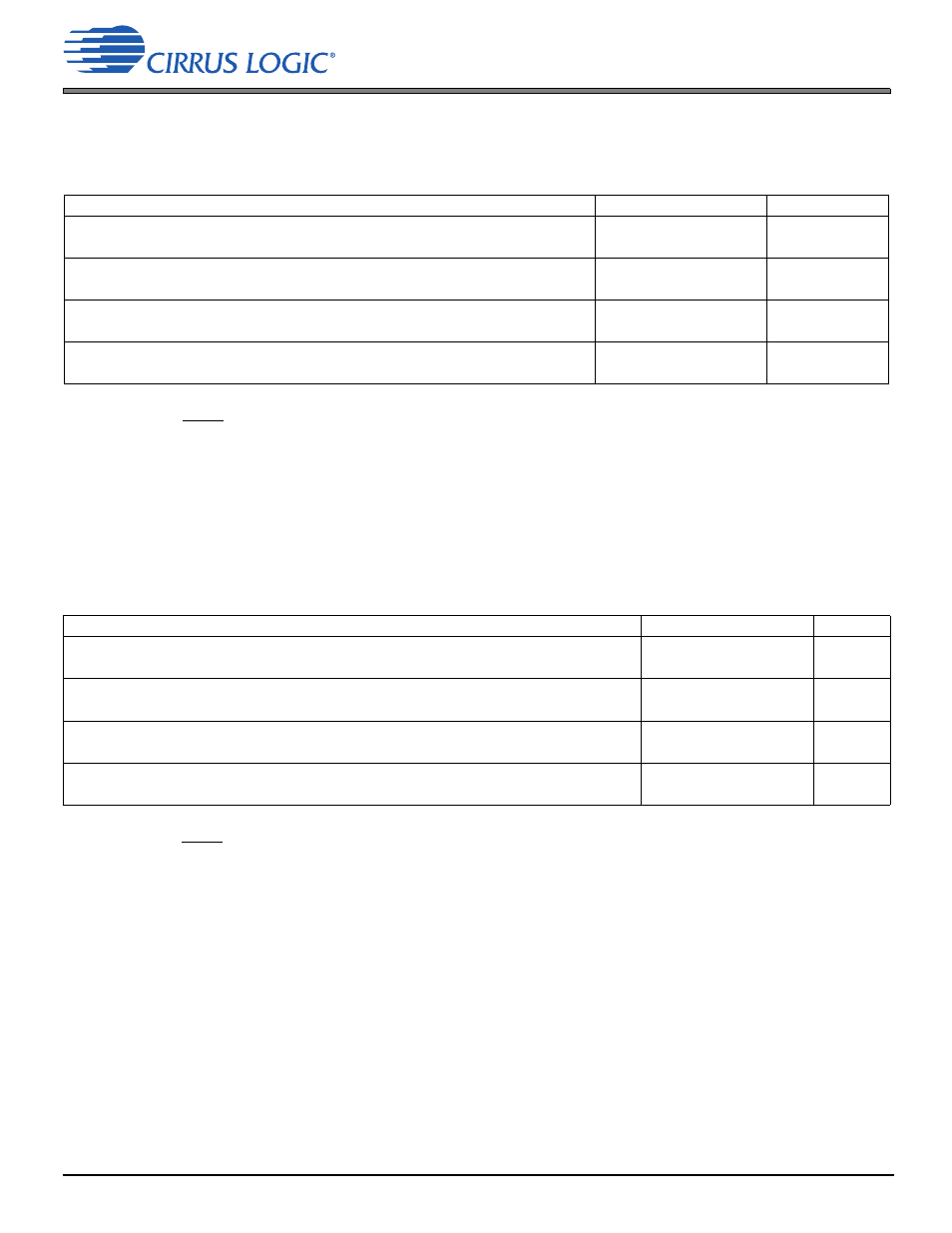

4.3 Power Supply Characteristics—1.0 V Power Dissipation

4.3 Power Supply Characteristics—1.0 V Power Dissipation

Test Conditions (unless otherwise specified): VD,VPLL=1.0 V, VL=1.8 V, GND = 0 V; all voltages with respect to GND.

T

A

= +25°C.

4.4 Power Supply Characteristics—1.2 V Power Dissipation

Test Conditions (unless otherwise specified): VD,VPLL=1.2 V, VL=1.8 V, GND = 0 V; all voltages with respect to GND.

T

A

= +25°C.

Parameters

Typical

Units

Core and I/O Operating

1

1.Characterized with O/S and MP3 decode running at 80 MHz, 6 MHz CLOCK driving PLL, MCLK slave, I²S data delivery.

VD + VPLL

2

2.VPLL exists only on the QFN package.The WLCSP package combines VD and VPLL into a single VD pin.

9.5

mA

VL

0.8

mA

RESET Active

3

3.Characterized with RESET driven low, CLOCK pin of CS48LV12/13 gated off, and all inputs to CS48LV12/13 driven to VL.

VD + VPLL

VL

1.8

mA

1.5

A

Hibernate Mode

4

4.The low-power mode used in this example is Hibernate mode. Characterized with DSP core halted, all memory banks powered down, PLL powered

down, and all internal clock domains gated off, CLOCK pin of CS48LV12/13 gated off, and all inputs to CS48LV12/13 driven to VL.

VD + VPLL

VL

11

A

0.147

A

Sleep Mode

5

5.The low-power mode used in this example is Sleep mode. Characterized with DSP core halted, all memory banks powered up, PLL powered down,

all internal clock domains gated off, CLOCK pin of CS48LV12/13 gated off, and all inputs to CS48LV12/13 driven to VL.

VD + VPLL

45

A

VL

0.147

A

Parameters

Typical

Units

Core and I/O Operating

1

1.Characterized with O/S and MP3 decode running at 80 MHz, 6 MHz CLOCK driving PLL, MCLK slave, I²S data delivery.

VD + VPLL

2

2.VPLL exists only on the QFN package. The WLCSP package combines VD and VPLL into a single VD pin.

12.0

mA

VL

0.8

mA

RESET Active

3

3.Characterized with RESET driven low, CLOCK pin of CS48LV12/13 gated off, and all inputs to CS48LV12/13 driven to VL.

VD + VPLL

VL

3.3

mA

1.5

A

Hibernate Mode

4

4.The low-power mode used in this example is Hibernate mode. Characterized with DSP core halted, all memory banks powered down, PLL powered

down, and all internal clock domains gated off, CLOCK pin of CS48LV12/13 gated off, and all inputs to CS48LV12/13 driven to VL.

VD + VPLL

VL

17

A

0.147

A

Sleep Mode

5

5.The low-power mode used in this example is Sleep mode. Characterized with DSP core halted, all memory banks powered up, PLL powered down,

all internal clock domains gated off, CLOCK pin of CS48LV12/13 gated off, and all inputs to CS48LV12/13 driven to VL.

VD + VPLL

75

A

VL

0.147

A