1 fsin domain clocking, Table 1. common dai_mclk frequencies, 2 fsout domain clocking – Cirrus Logic CS44600 User Manual

Page 24: Figure 14. fundamental mode crystal configuration, 1 fsin domain clocking 4.3.2 fsout domain clocking, Figure 14.fundamental mode crystal configuration

24

DS633F1

CS44600

4.3.1

FsIn Domain Clocking

Common DAI_MCLK frequencies and sample rates are shown in

.

4.3.2

FsOut Domain Clocking

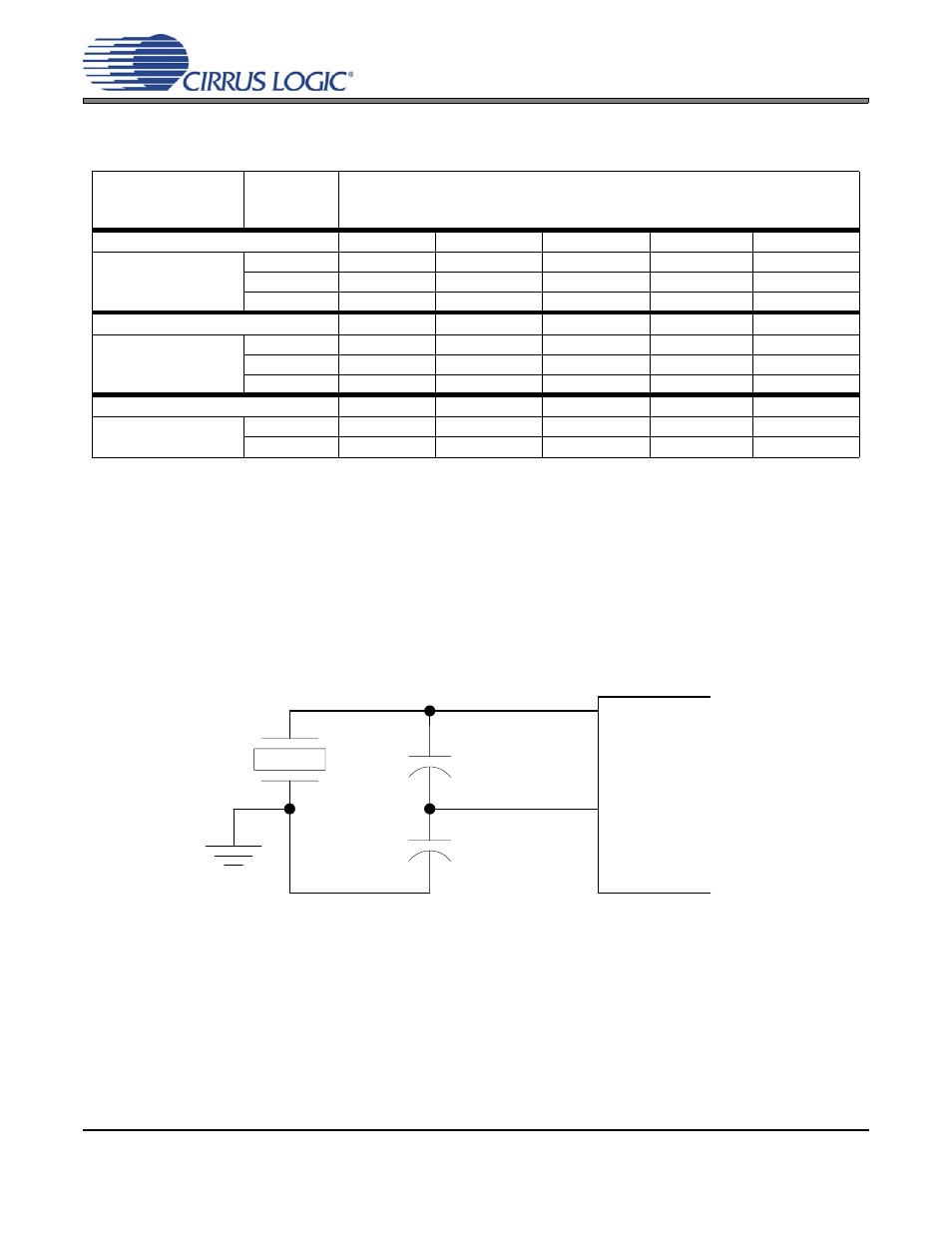

To ensure the highest quality conversion of PWM signals, the CS44600 is capable of operating from a

fundamental mode or 3

rd

overtone crystal, or a clock signal attached to XTI, at a frequency of 24.576 MHz

to 54 MHz. If XTI is being directly driven by a clock signal, XTO can be left floating or tied to ground

through a pull-down resistor and the internal oscillator should be powered down using the PDN_XTAL bit

in register 02h.

Mode

(sample-rate range)

Sample

Rate

(kHz)

DAI_MCLK (MHz)

DAI_MCLK/LRCK Ratio

−>

256x

384x

512x

768x

1024x

Single Speed

(4 to 50 kHz)

32

8.1920

12.2880

16.3840

24.5760

32.7680

44.1

11.2896

16.9344

22.5792

33.8688

45.1584

48

12.2880

18.4320

24.5760

36.8640

49.1520

DAI_MCLK/LRCK Ratio

−>

128x

192x

256x

384x

512x

Double Speed

(50 to 100 kHz)

64

8.1920

12.2880

16.3840

24.5760

32.7680

88.2

11.2896

16.9344

22.5792

33.8688

45.1584

96

12.2880

18.4320

24.5760

36.8640

49.1520

DAI_MCLK/LRCK Ratio

−>

64x

96x

128x

192x

256x

Quad Speed

(100 to 200 kHz)

176.4

n/a

n/a

22.5792

33.8688

45.1584

192

n/a

n/a

24.5760

36.8640

49.1520

Table 1. Common DAI_MCLK Frequencies

Y1

C1

C2

XTI

XTO

Figure 14. Fundamental Mode Crystal Configuration