3 mode control 3 (address 03h), 1 soft ramp and zero cross control (szc), Table 6. digital interface formats - dsd mode – Cirrus Logic CS4382A User Manual

Page 35: Cs4382a

DS618F2

35

CS4382A

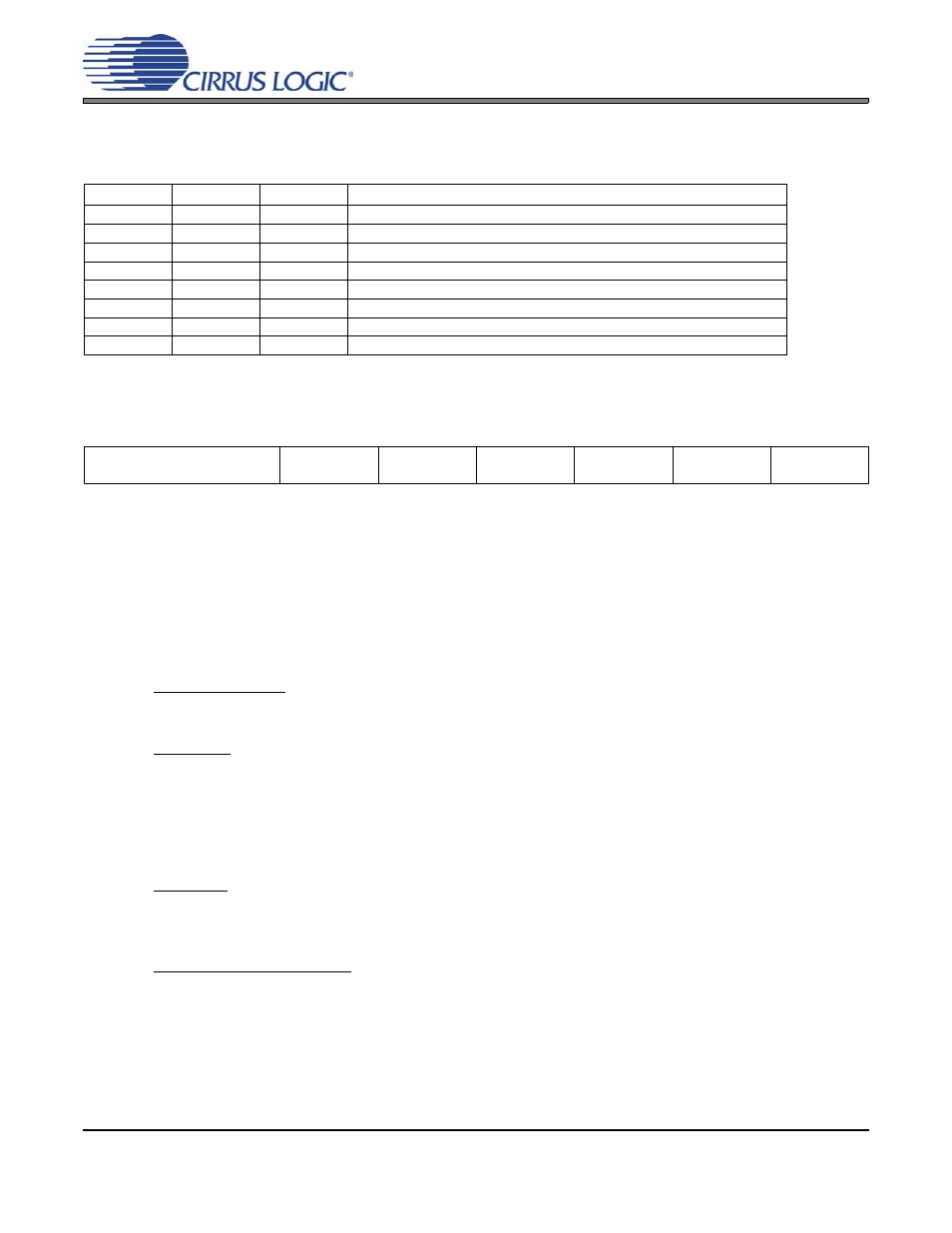

DSD Mode:

The relationship between the oversampling ratio of the DSD audio data and the required

master clock-to-DSD-data-rate is defined by the Digital Interface Format pins.

6.3

Mode Control 3 (Address 03h)

6.3.1

Soft Ramp and Zero Cross Control (SZC)

Default = 10

00 - Immediate Change

01 - Zero Cross

10 - Soft Ramp

11 - Soft Ramp on Zero Crossings

Function:

Immediate Change

When Immediate Change is selected, all level changes will take effect immediately in one step.

Zero Cross

Zero Cross Enable dictates that signal level changes, either by attenuation changes or muting, will occur

on a signal zero crossing to minimize audible artifacts. The requested level change will occur after a time-

out period between 512 and 1024 sample periods (10.7 ms to 21.3 ms at 48 kHz sample rate) if the signal

does not encounter a zero crossing. The zero cross function is independently monitored and implemented

for each channel.

Soft Ramp

Soft Ramp allows level changes, both muting and attenuation, to be implemented by incrementally ramp-

ing, in 1/8 dB steps, from the current level to the new level at a rate of 1 dB per 8 left/right clock periods.

Soft Ramp on Zero Crossing

Soft Ramp and Zero Cross Enable dictates that signal level changes, either by attenuation changes or

muting, will occur in 1/8 dB steps and be implemented on a signal zero crossing. The 1/8 dB level change

will occur after a time-out period between 512 and 1024 sample periods (10.7 ms to 21.3 ms at 48 kHz

sample rate) if the signal does not encounter a zero crossing. The zero cross function is independently

monitored and implemented for each channel.

DIF2

DIF1

DIFO

DESCRIPTION

0

0

0

64x oversampled DSD data with a 4x MCLK to DSD data rate

0

0

1

64x oversampled DSD data with a 6x MCLK to DSD data rate

0

1

0

64x oversampled DSD data with a 8x MCLK to DSD data rate

0

1

1

64x oversampled DSD data with a 12x MCLK to DSD data rate

1

0

0

128x oversampled DSD data with a 2x MCLK to DSD data rate

1

0

1

128x oversampled DSD data with a 3x MCLK to DSD data rate

1

1

0

128x oversampled DSD data with a 4x MCLK to DSD data rate

1

1

1

128x oversampled DSD data with a 6x MCLK to DSD data rate

Table 6. Digital Interface Formats - DSD Mode

7

6

5

4

3

2

1

0

SZC1

SZC0

SNGLVOL

RMP_UP

MUTEC+/-

AMUTE

Reserved

MUTEC

1

0

0

0

0

1

0

0