4 oversampling modes, 5 interpolation filter, 6 de-emphasis – Cirrus Logic CS4382A User Manual

Page 24: Cs4382a

24

DS618F2

CS4382A

4.4

Oversampling Modes

The CS4382A operates in one of three oversampling modes based on the input sample rate. Mode selection

is determined by the DSD_EN, M3, and M2 pins in Hardware Mode or the FM bits in Software Mode. Single-

speed mode supports input sample rates up to 50 kHz and uses a 128x oversampling ratio. Double-speed

Mode supports input sample rates up to 100 kHz and uses an oversampling ratio of 64x. Quad-speed Mode

supports input sample rates up to 200 kHz and uses an oversampling ratio of 32x.

4.5

Interpolation Filter

To accommodate the increasingly complex requirements of digital audio systems, the CS4382A incorpo-

rates selectable interpolation filters for each mode of operation. A “fast” and a “slow” roll-off filter is available

in each of Single, Double, and Quad-Speed modes. These filters have been designed to accommodate a

variety of musical tastes and styles. The FILT_SEL bit is used to select which filter is used (see the

for more details).

When in Hardware Mode, only the “fast” roll-off filter is available.

Filter specifications can be found in

, and filter response plots can be found in

to

.

4.6

De-emphasis

The CS4382A includes on-chip digital de-emphasis filters. The de-emphasis feature is included to accom-

modate older audio recordings that utilize pre-emphasis equalization as a means of noise reduction.

shows the de-emphasis curve. The frequency response of the de-emphasis curve will scale pro-

portionally with changes in sample rate (Fs) if the input sample rate does not match the coefficient which

has been selected.

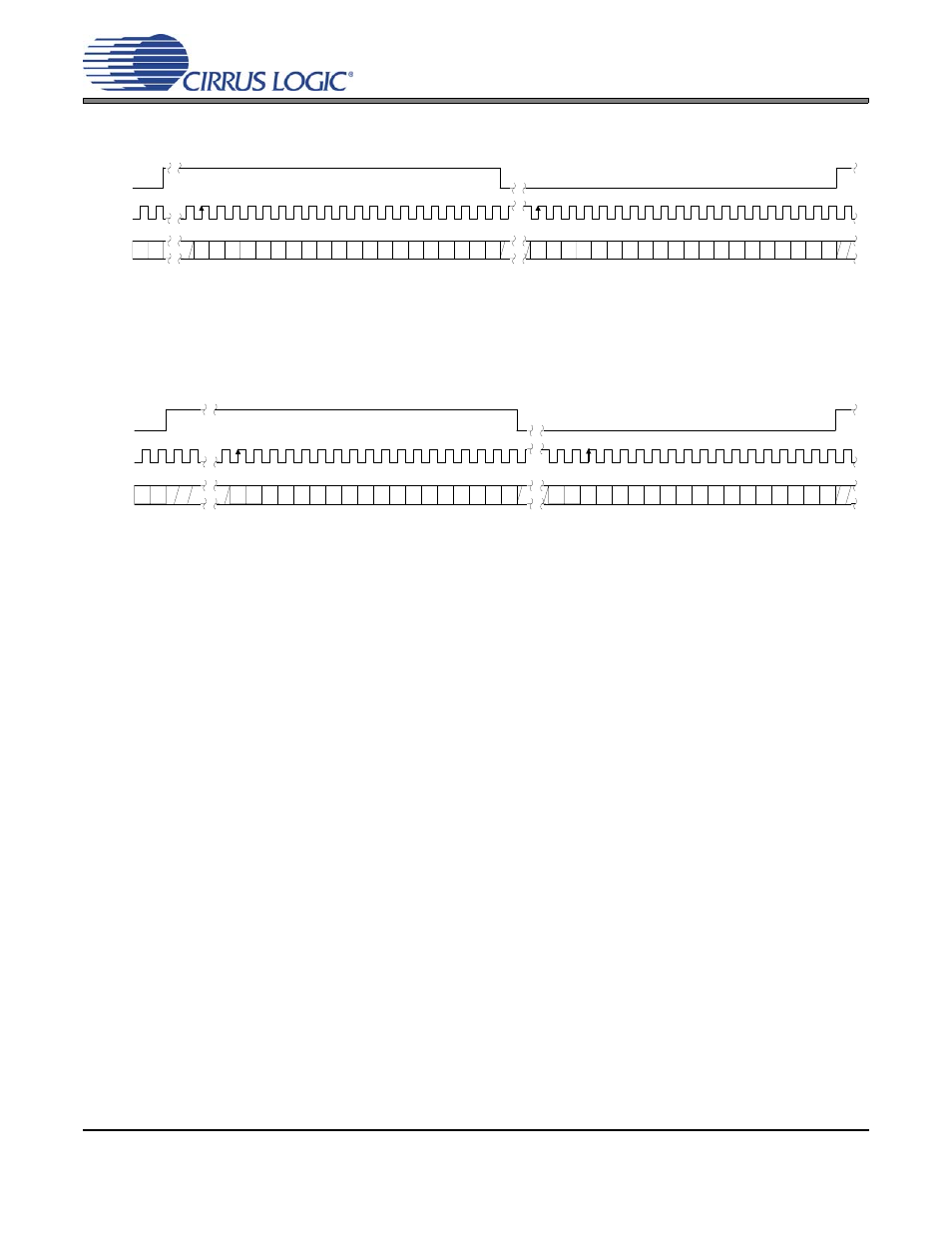

LRCK

SCLK

Left Channel

Right Channel

SDINx

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

1

0

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

17 16

17 16

32 clocks

19 18

19 18

Figure 11. Format 4 - Right-Justified 20-bit Data

LRCK

SCLK

Left Channel

Right Channel

SDINx

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

1

0

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

17 16

17 16

32 clocks

Figure 12. Format 5 - Right-Justified 18-bit Data