Cirrus Logic CS43122 User Manual

Advance product information, Features, Description

Advance Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

1

Copyright

Cirrus Logic, Inc. 2000

(All Rights Reserved)

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

CS43122

122 dB, 24-Bit, 192 kHz DAC for Digital Audio

Features

l

24 Bit Conversion

l

Up to 192 kHz Sample Rates

l

122 dB Dynamic Range

l

-102 dB THD+N

l

Second-Order Dynamic-Element Matching

l

Low Clock Jitter Sensitivity

l

102 dB Stop-band attenuation

l

Single +5 V supply

l

Soft Mute Control

l

Digital De-Emphasis for 32, 44.1, and 48 kHz

l

External Reference Input

l

Pin-compatible with the CS4396

Description

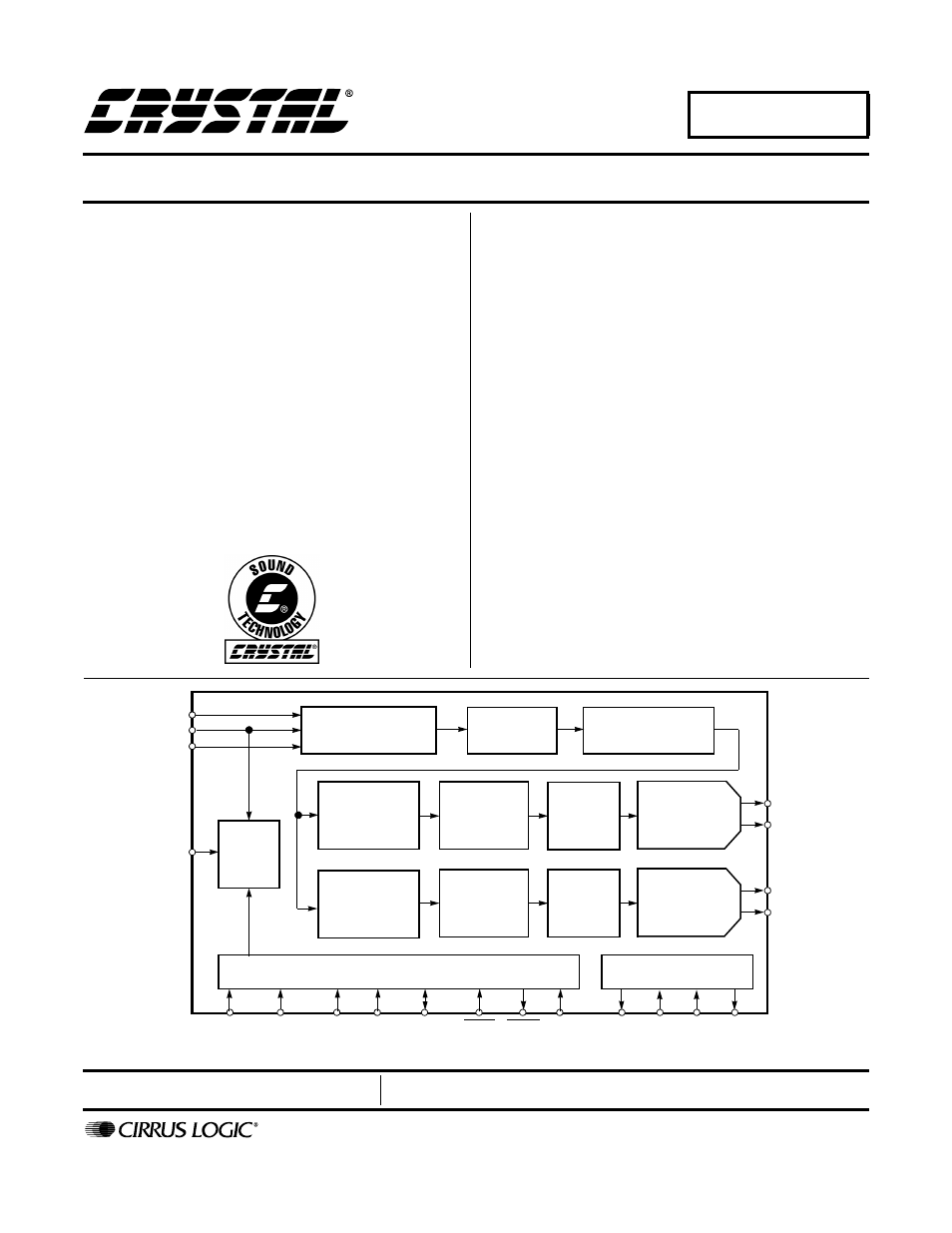

The CS43122 is a complete high performance 24 bit-

192 kHz stereo digital-to-analog conversion system. The

device includes a digital interpolation filter followed by an

oversampled 5 bit delta-sigma modulator which drives

second generation dynamic-element-matching (DEM)

selection logic. The output from the DEM block controls

the input to a multi-element switched capacitor DAC/low-

pass filter, with fully-differential outputs. This multi-bit ar-

chitecture features significantly lower out-of-band noise

and jitter sensitivity than traditional 1-bit designs, and the

advanced second generation DEM guarantees low noise

and distortion at all signal levels.

The CS43122 is the optimal D/A converter solution for

any application that requires the highest performance

and best possible sound quality including high-end con-

sumer and professional audio products such as

Universal DVD players, A/V receivers, Outboard D/A

Converters, CD Players, and Mixing Consoles.

ORDERING INFORMATION

CS43122-KS -10° to 70° C 28-pin SOIC

CDB43122

Evaluation Board

SCLK

MCLK

M4

LRCK

SDATA

AOUTL+

AOUTR+

SERIAL INTERFACE

AND FORMAT SELECT

INTERPOLATION

SOFT MUTE

∆Σ

MODULATOR

DYNAMIC

DE-EMPHASIS

SWITCHED

AOUTL-

AOUTR-

FILT+

FILTER

INTERPOLATION

FILTER

FILTER

MULTI-BIT

∆Σ

MODULATOR

MULTI-BIT

ELEMENT

MATCHING

LOGIC

DYNAMIC

ELEMENT

MATCHING

LOGIC

CAPACITOR-DAC

AND FILTER

SWITCHED

CAPACITOR-DAC

AND FILTER

VREF

CMOUT

FILT-

VOLTAGE REFERENCE

HARDWARE MODE CONTROL

CLOCK

DIVIDER

(CONTROL PORT)

(AD0/CS)

M3

M2

(AD1/CDIN) (SCL/CCLK)

M1

M0

(SDA/CDOUT)

RESET

MUTEC MUTE

DEC ‘00

DS526PP2

Document Outline

- CS43122

- Features

- Description

- Table of Contents

- List of Figures

- List of Tables

- 1. Characteristics/Specifications

- 2. Typical Connection Diagram

- 3. Register Description

- 4. Pin Description

- 5. Applications

- 6. Control Port Interface

- 6.1 SPI Mode

- 6.2 2 Wire Mode

- 6.3 Memory Address Pointer (MAP)

- Table 4. Operational Mode 0 (16 to 55 kHz) Digital Interface Format Options

- Table 5. Operational Mode 0 (16 to 55 kHz) De-Emphasis Options

- Table 6. Operational Mode 1 (45 to 105 kHz) Sample Rate Mode Options

- Table 7. Operational Mode 2 (95 to 200 kHz) Sample Rate Mode Options

- Figure 7. Operational Mode 0 Transition Band

- Figure 8. Operational Mode 0 Stopband Rejection

- Figure 9. Operational Mode 0 Transition Band

- Figure 10. Operational Mode 0 Frequency Response

- Figure 11. Operational Mode 0 Stopband

- Figure 12. Operational Mode 0 Transition Band

- Figure 13. Operational Mode 0 Transition Band

- Figure 14. Operational Mode 0 Frequency Response

- Figure 15. Operational Mode 2 Stopband Rejection

- Figure 16. Operational Mode 2 Transition Band

- Figure 17. Operational Mode 2 Transition Band

- Figure 18. Operational Mode 2 Frequency Response

- Figure 19. De-Emphasis Curve

- Figure 20. Format 0, Left Justified

- Figure 21. Format 1, I2S

- Figure 22. Format 2, Right Justified, 16-Bit Data

- Figure 23. Format 3, Right Justified, 24-Bit Data

- 7. Parameter Definitions

- 8. References

- 9. Package Dimensions