Ordering information, Revision history, Ordering information 13. revision history – Cirrus Logic CS4270 User Manual

Page 44

44

DS686F1

CS4270

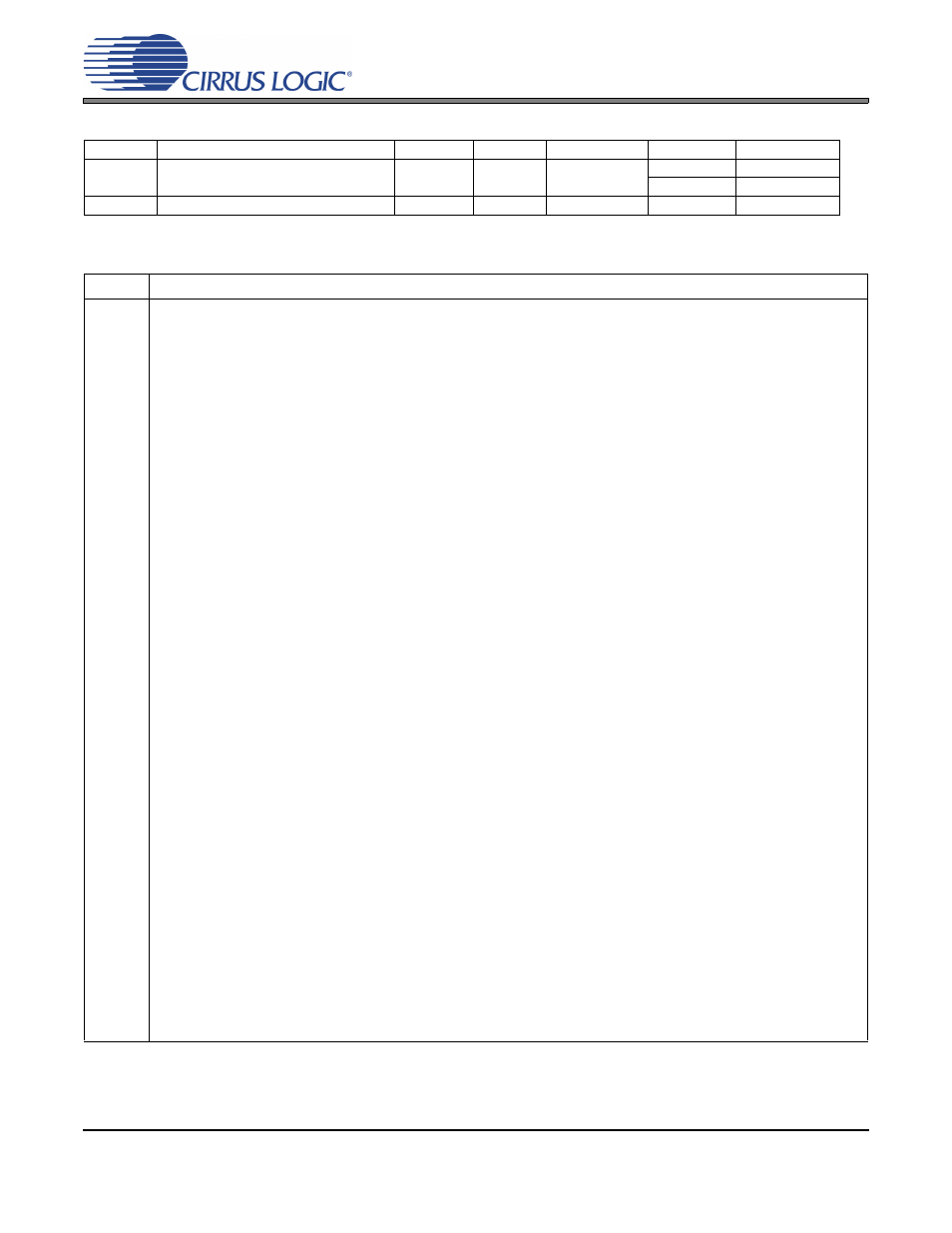

12.ORDERING INFORMATION

13.REVISION HISTORY

Product

Description

Package

Pb-Free

Temp Range

Container

Order #

CS4270 24-Bit 192 kHz Stereo Audio CODEC 24-TSSOP

YES

-10° to +70° C

Rail

CS4270-CZZ

Tape & Reel CS4270-CZZR

CDB4270

CS4270 Evaluation Board

-

-

-

-

CDB4270

Release

Changes

F1

–

Deleted automotive grade content and references to grade throughout.

–

Formatting changes throughout.

–

Updated several

–

Added

“Digital I/O Pin Characteristics” on page 6

Added decoupling cap to VLC on Typical Connection Diagram,

–

Performance specifications updated per measured data in

Section 4. “Characteristics and

:

– Min

Specified Operating Conditions

for

“DC Power Supplies:” on page 8

.

– Typ and Max

for

“Total Harmonic Distortion + Noise” on page 9

“Total Harmonic Distortion + Noise” on page 11

.

– Typ

“Interchannel Isolation” on page 11

– Typ and Max

“Power Supply Current” on page 13

.

– Typ and Max

“Power Consumption VA = 5 V, VD = VLC=

.

– Typ

“FILT+ Output Impedance” on page 13

.

– Min

Switching Characteristics - Software Mode - SPI Format

for

and

–

Added

“Acknowledge Delay from SCL Falling” on page 17

–

Transition Time from CCLK to CDOUT Valid (Note 21)

to

“Switching Characteristics - Software Mode - SPI Format” on page 18.

–

Added CDOUT to

.

–

Added

and associated text in

Section 5.1.1 Access to Stand-Alone Mode

–

Added

–

Updated descriptions of recommended power-up sequences in

–

Updated

“Clock Ratio Selection” on page 22

(added all SCLK/LRCK ratios to the serial control

–

Updated

Section 5.2.7 “DC Offset Calibration Using the High-Pass Filter” on page 23

Section 5.3 “Popguard Transient Control” on page 24

.

–

Updated

Section 5.5.1 “Input Component Values” on page 25

–

Updated presentation of input source resistance plots (

–

Added

Section 6.2.2 SPI Read on page 30

.

–

Section 7. “Register Quick Reference” on page 31

Section 8.3.2 “Ratio Select (Bits 3:1)” on page 33

.

–

Updated

Section 8.3.3 “Popguard Transient Control (Bit 0)” on page 33

–

Updated

–

Updated