3 mode control - address 03h, Table 9. functional mode selection, 2 ratio select (bits 3:1) – Cirrus Logic CS4270 User Manual

Page 33: Table 10. mclk divider configuration, 3 popguard transient control (bit 0), Section 8.3.3, P 33, Cs4270

DS686F1

33

CS4270

8.3

Mode Control - Address 03h

8.3.1

ADC Functional Mode & Master/Slave Mode (Bits 5:4)

Function:

In Master Mode, the user must configure the CS4270 Speed Mode with these bits. In Slave Mode, the

CS4270 auto-detects the speed mode.

8.3.2

Ratio Select (Bits 3:1)

Function:

These bits are used to select the clocking ratios. The PDN bit should be set before, and cleared after, any

changes to these bits.

8.3.3

Popguard Transient Control (Bit 0)

Function:

When set, the Popguard Transient Control allows the quiescent voltage to slowly ramp to and from AGND

to the quiescent voltage during power-on or power-off when this function is set. When cleared (default),

this function is disabled. See

for additional details about Popguard.

7

6

5

4

3

2

1

0

Reserved

Reserved

FM1

FM0

MCLK_FREQ2 MCLK_FREQ1 MCLK_FREQ0

POPG

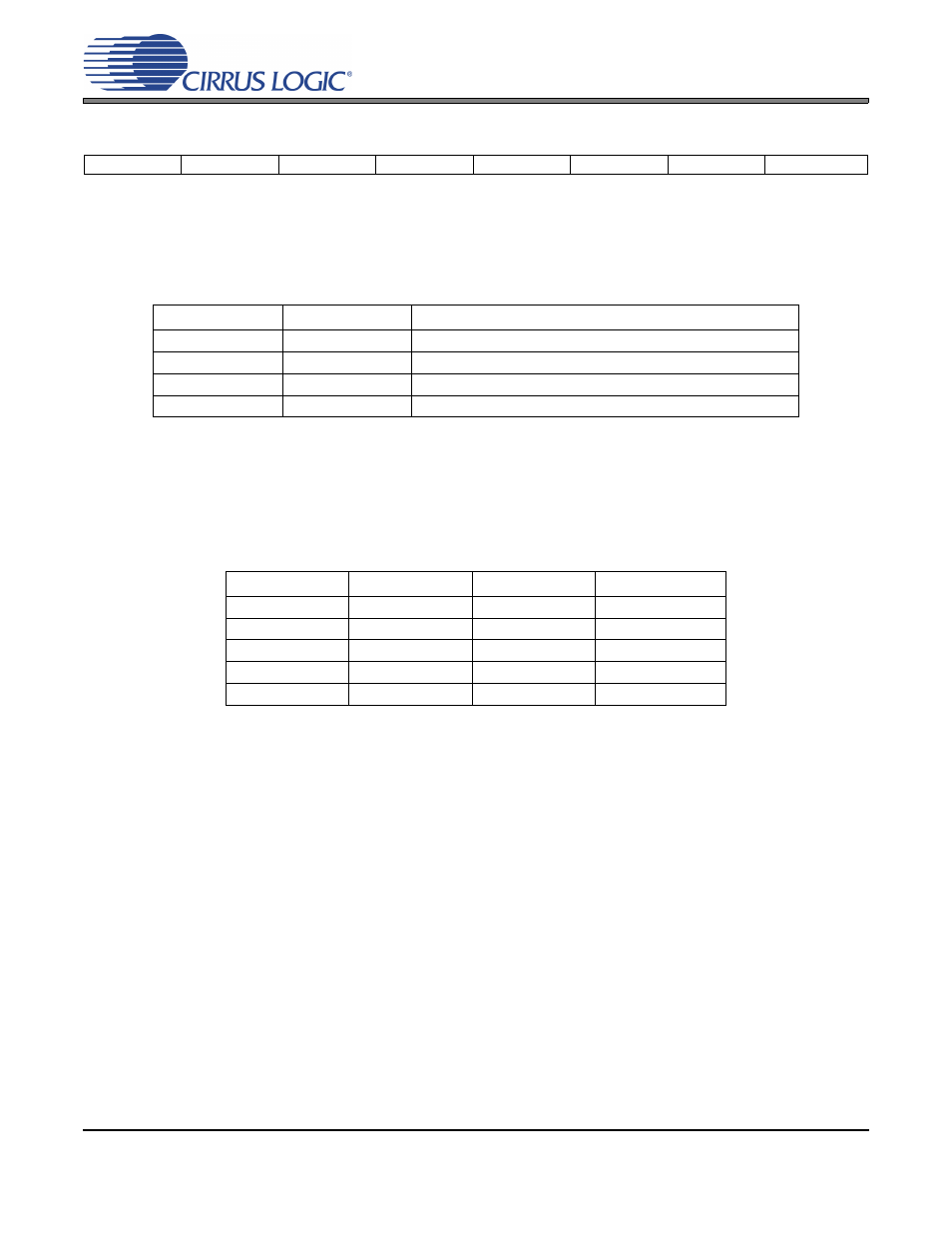

FM1

FM0

Mode

0

0

Single-Speed Master Mode: 4 to 54 kHz sample rates

0

1

Double-Speed Master Mode: 50 to 108 kHz sample rates

1

0

Quad-Speed Master Mode: 100 to 216 kHz sample rates

1

1

Slave Mode (default)

Table 9. Functional Mode Selection

MCLK_FREQ2

MCLK_FREQ1

MCLK_FREQ0

Mode

0

0

0

Divide by 1 (default)

0

0

1

Divide by 1.5

0

1

0

Divide by 2

0

1

1

Divide by 3

1

0

0

Divide by 4

Table 10. MCLK Divider Configuration