Table 10. adc digital interface formats, 3 mute adc (bit 2), 4 adc high-pass filter freeze (bit 1) – Cirrus Logic CS4265 User Manual

Page 39: 5 master / slave mode (bit 0), 5 mclk frequency - address 05h, 1 master clock dividers (bits 6:4), Table 11. mclk frequency, Bits (see, Mclk frequency - address 05h, Table 10

DS657F3

39

CS4265

6.4.3

Mute ADC (Bit 2)

Function:

When this bit is set, the serial audio output of the both ADC channels is muted.

6.4.4

ADC High-Pass Filter Freeze (Bit 1)

Function:

When this bit is set, the internal high-pass filter is disabled. The current DC offset value will be frozen and

continue to be subtracted from the conversion result. See

“High-Pass Filter and DC Offset Calibration” on

6.4.5

Master / Slave Mode (Bit 0)

Function:

This bit selects either master or slave operation for the serial audio port. Setting this bit selects Master

Mode, while clearing this bit selects Slave Mode.

6.5

MCLK Frequency - Address 05h

6.5.1

Master Clock Dividers (Bits 6:4)

Function:

Sets the frequency of the supplied MCLK signal. See

for the appropriate settings.

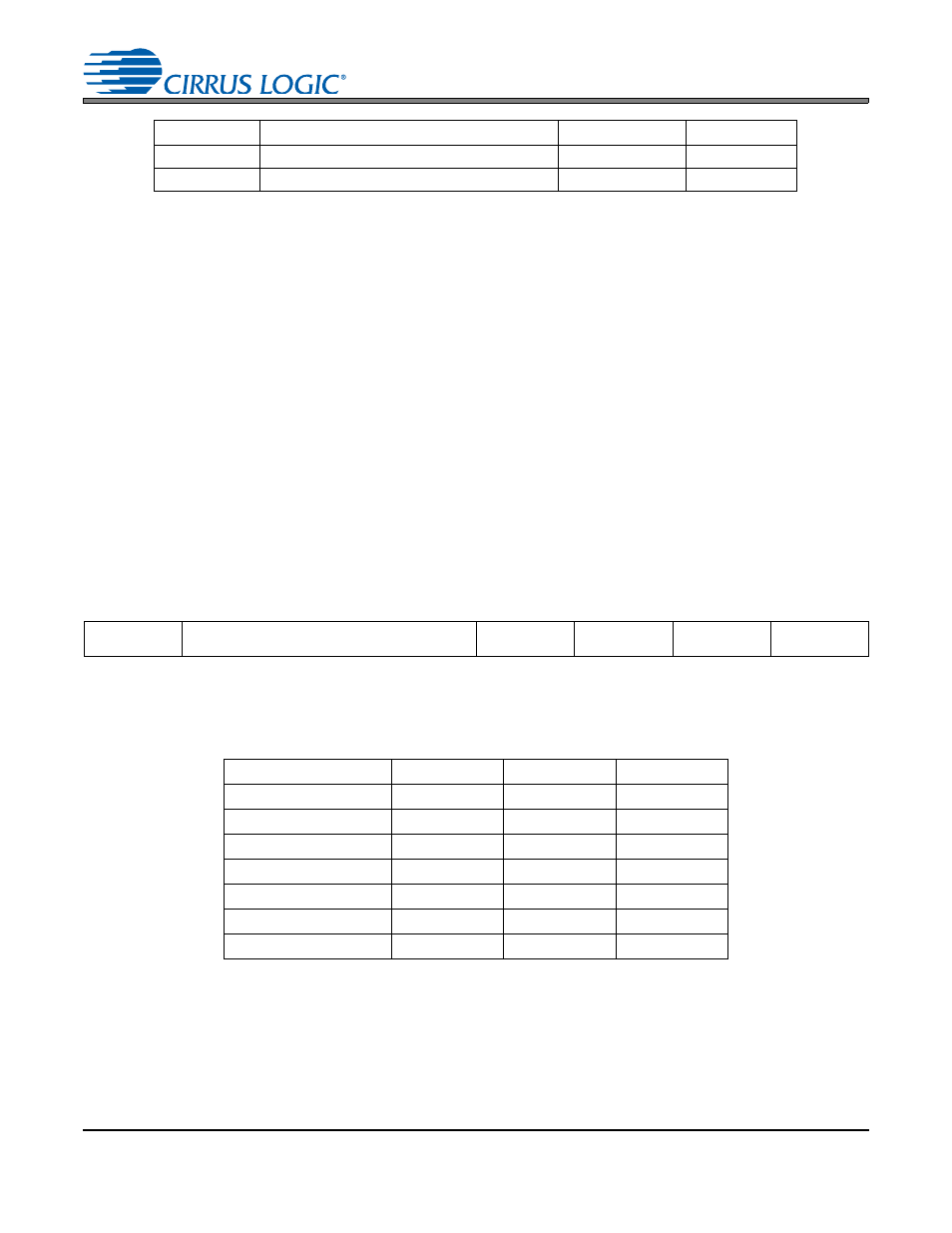

ADC_DIF

Description

Format

Figure

0

Left-Justified, up to 24-bit data (default)

0

1

I²S, up to 24-bit data

1

Table 10. ADC Digital Interface Formats

7

6

5

4

3

2

1

0

Reserved

MCLK

Freq2

MCLK

Freq1

MCLK

Freq0

Reserved

Reserved

Reserved

Reserved

MCLK Divider

MCLK Freq2

MCLK Freq1

MCLK Freq0

ч 1

0

0

0

ч 1.5

0

0

1

ч 2

0

1

0

ч 3

0

1

1

ч 4

1

0

0

Reserved

1

0

1

Reserved

1

1

x

Table 11. MCLK Frequency