3 subclock source control - address 03h, Table 3. dac subclock source, Table 4. adc subclock source – Cirrus Logic CDB4245 User Manual

Page 13: Cdb4245

CDB4245

DS656DB1

13

6.3

SUBCLOCK SOURCE CONTROL - ADDRESS 03H

6.3.1

DAC SUBCLOCK SOURCE (BITS 5:4)

Default = 01

Function:

These bits select the source of the CS4245 SCLK2 and LRCK2 signals. Table 3 shows the available

settings.

6.3.2

ADC SUBCLOCK SOURCE (BITS 1:0)

Default = 01

Function:

This bit selects the source of the CS4245 SCLK1 andLRCK1 signals. Table 4 shows the available set-

tings.

7

6

5

4

3

2

1

0

Reserved

Reserved

DAC1

DAC0

Reserved

Reserved

ADC1

ADC0

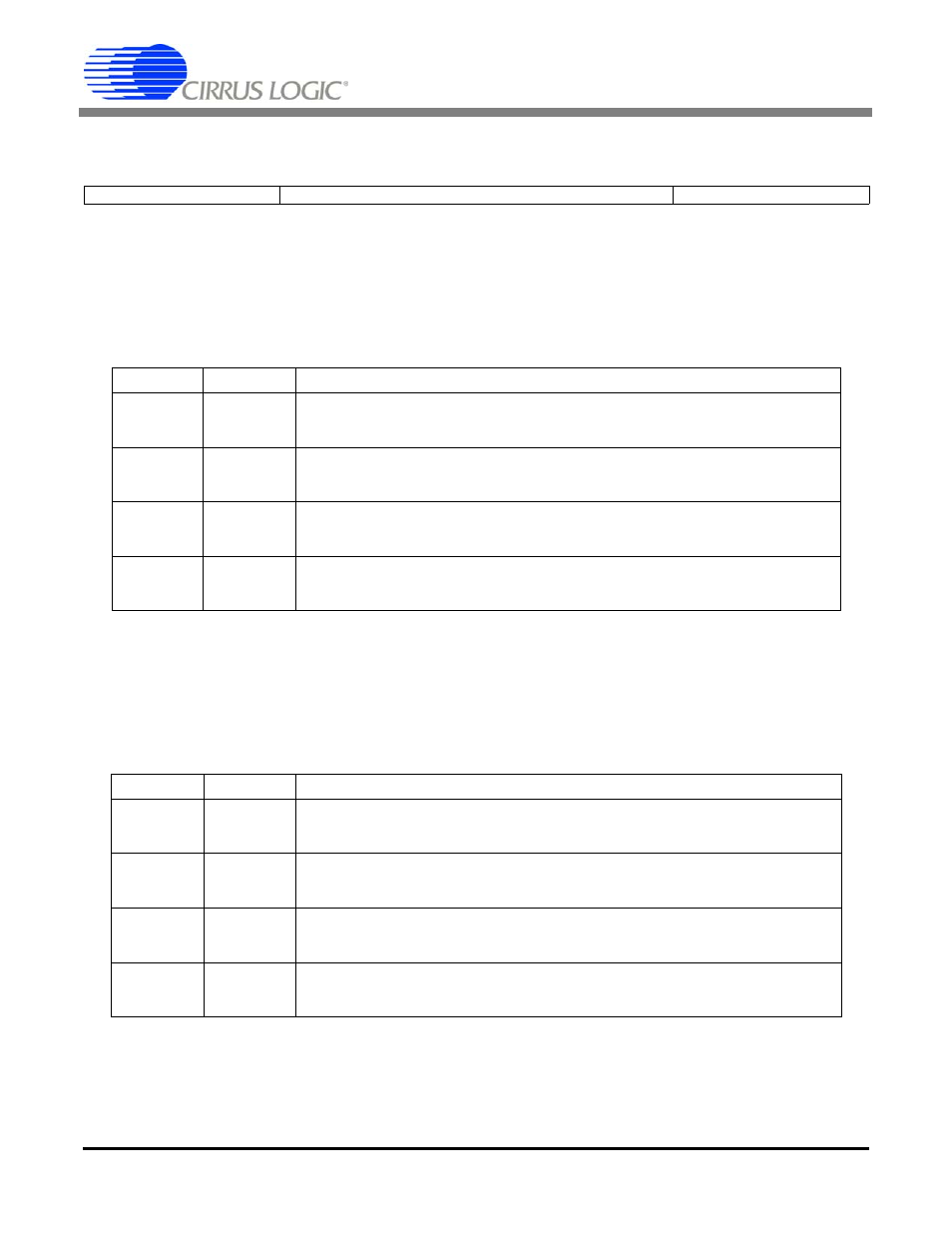

Table 3. DAC Subclock Source

DAC1

DAC0

DAC Subclock Source

0

0

- CS4245 is Master

- CS8416 is Slave to CS4245

- Header 2 Subclocks are Output from CS4245

0

1

- CS4245 is Slave to CS8416

- CS8416 is Master

- Header 2 Subclocks are Output from CS8416

1

0

- CS4245 is Slave to Header

- CS8416 is Slave to Header

- Header 2 subclocks are an Input

1

1

- CS4245 is Slave to ADC subclocks

- CS8416 is Slave to ADC subclocks

- Header 2 Subclocks are Output from ADC subclocks

Table 4. ADC Subclock Source

ADC1

ADC0

ADC Subclock Source

0

0

- CS4245 is Master

- CS8406 is Slave to CS4245

- Header 1 Subclocks are Output from CS4245

0

1

- CS4245 is Slave to CS8406

- CS8406 is Master

- Header 1 Subclocks are Output from CS8406

1

0

- CS4245 is Slave to Header

- CS8406 is Slave to Header

- Header 1 subclocks are an Input

1

1

- CS4245 is Slave to DAC subclocks

- CS8406 is Slave to DAC subclocks

- Header 1 Subclocks are Output from DAC subclocks