2 digital filter, Crd5378 – Cirrus Logic CRD5378 User Manual

Page 35

CRD5378

DS639RD2

35

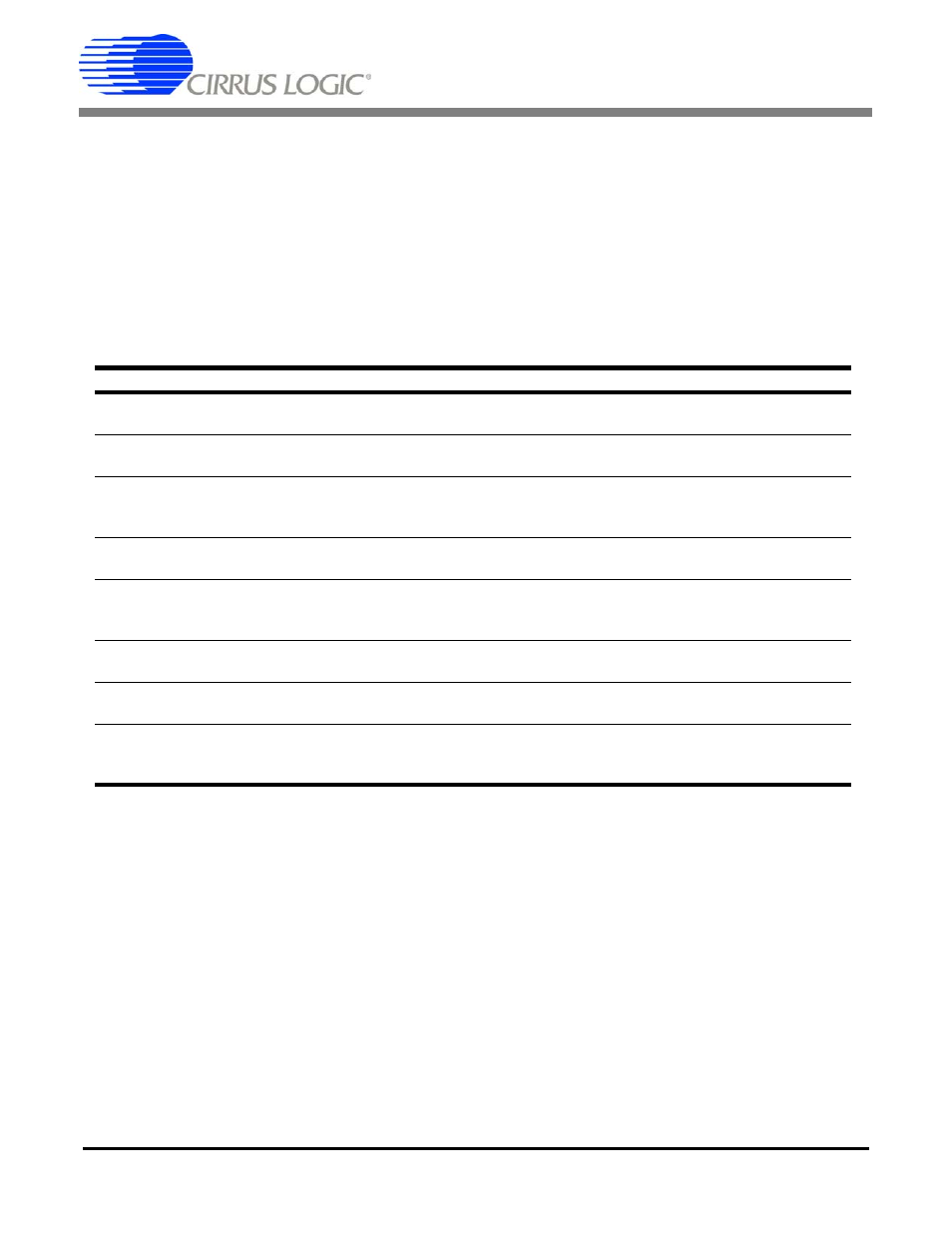

3.3.2

Digital Filter

The Digital Filter sub-panel sets up the digital filter configuration options.

By default the Digital Filter sub-panel configures the system to use on-chip coefficients and test bit

stream data. The on-chip data can be overwritten by loading custom coefficients and test bit stream data

from the Customize sub-panel on the Control panel.

Any changes made under this sub-panel will not be applied to the target board until the Configure button

is pushed. The Configure button writes the new configuration to the target board and then enables the

data Capture button.

Control

Description

Channel Set

Selects the number of channels that are enabled in the digital filter. For the CS5378

digital filter, only 1 can be enabled.

Output Rate

Selects the output word rate of the digital filter. Output word rates from 4000 SPS to

1 SPS (0.25 mS to 1 S) are available.

Output Filter

Selects the output filter stage from the digital filter. Sinc output, FIR1 output, FIR2

output, IIR 1st order output, IIR 2nd order output, or IIR 3rd order output can be

selected. FIR2 output provides full decimation of the modulator data.

FIR Coeff

Selects the on-chip FIR coefficient set to use in the digital filter. Linear phase or min-

imum phase FIR coefficients can be selected.

IIR Coeff

Selects the on-chip IIR coefficient set to use in the digital filter. Coefficient sets pro-

ducing a 3 Hz high-pass corner at 2000 SPS, 1000 SPS, 500 SPS, 333 SPS, and

250 SPS can be selected.

Filter Clock

Sets the digital filter internal clock rate. Lower internal clock rates can save power

when using slow output word rates.

MCLK Rate

Sets the analog sample clock rate. The CS5373A modulator and test DAC typically

run with MCLK set to 2.048 MHz.

Configure

Writes all information from the Setup panel to the digital filter. The data Capture but-

ton becomes available once the configuration information is written to the target

board.