Analog Devices ADSP-21020 User Manual

Page 9

ADSP-21020

REV. C

–9–

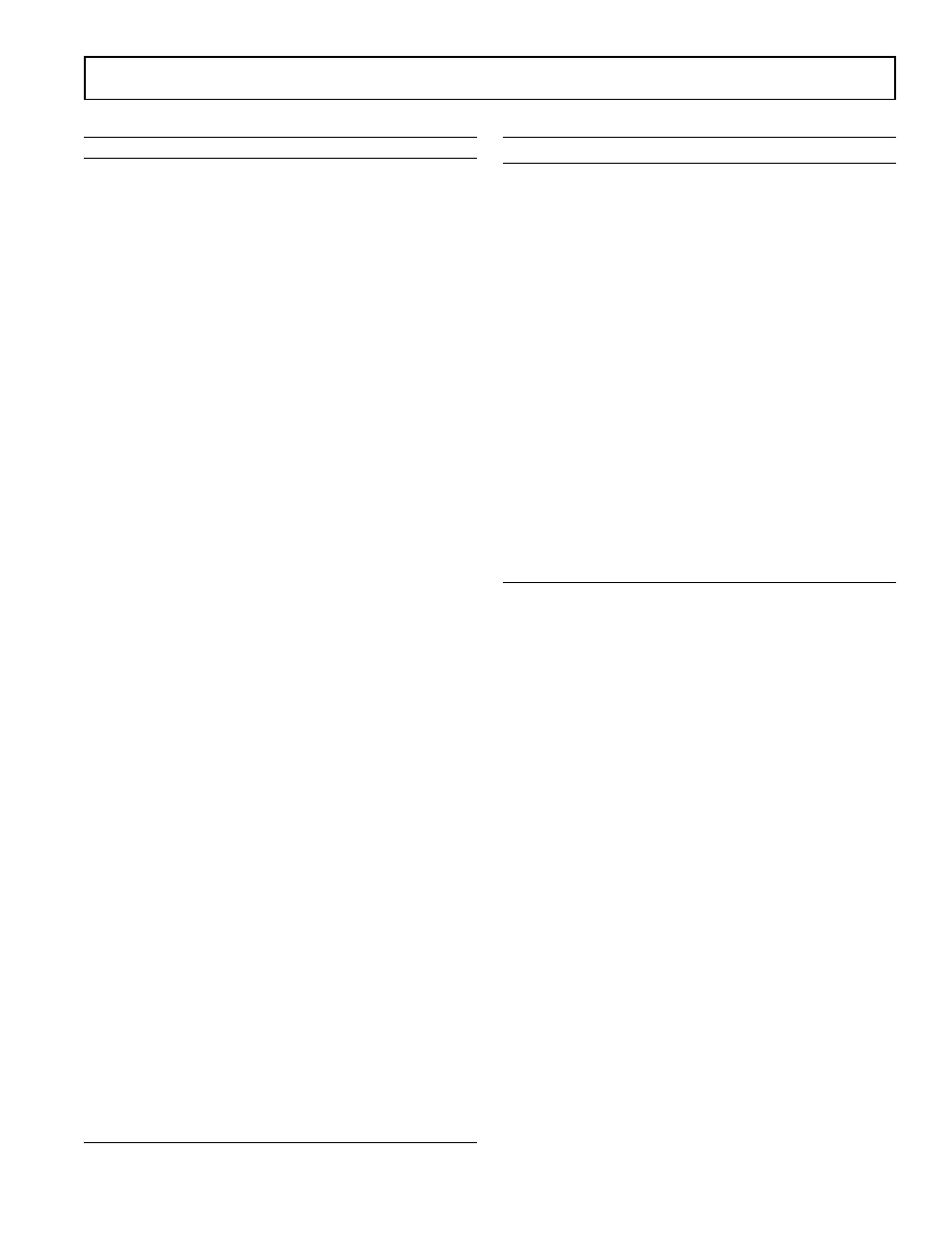

Table III. Universal Registers

Name

Function

Register File

R15–R0

Register file locations

Program Sequencer

PC*

Program counter; address of instruction cur-

rently executing

PCSTK

Top of PC stack

PCSTKP

PC stack pointer

FADDR*

Fetch address

DADDR*

Decode address

LADDR

Loop termination address, code; top of loop

address stack

CURLCNTR

Current loop counter; top of loop count stack

LCNTR

Loop count for next nested counter-controlled

loop

Data Address Generators

I7–I0

DAG1 index registers

M7–M0

DAG1 modify registers

L7–L0

DAG1 length registers

B7–B0

DAG1 base registers

I15–I8

DAG2 index registers

M15–M8

DAG2 modify registers

L15–L8

DAG2 length registers

B15–B8

DAG2 base registers

Bus Exchange

PX1

PMD-DMD bus exchange 1 (16 bits)

PX2

PMD-DMD bus exchange 2 (32 bits)

PX

48-bit PX1 and PX2 combination

Timer

TPERIOD

Timer period

TCOUNT

Timer counter

Memory Interface

DMWAIT

Wait state and page size control for data

memory

DMBANK1

Data memory bank 1 upper boundary

DMBANK2

Data memory bank 2 upper boundary

DMBANK3

Data memory bank 3 upper boundary

DMADR*

Copy of last data memory address

PMWAIT

Wait state and page size control for program

memory

PMBANK1

Program memory bank 1 upper boundary

PMADR*

Copy of last program memory address

System Registers

MODE1

Mode control bits for bit-reverse, alternate reg-

isters, interrupt nesting and enable, ALU satu-

ration, floating-point rounding mode and

boundary

MODE2

Mode control bits for interrupt sensitivity,

cache disable and freeze, timer enable, and I/O

flag configuration

IRPTL

Interrupt latch

IMASK

Interrupt mask

IMASKP

Interrupt mask pointer (for nesting)

ASTAT

Arithmetic status flags, bit test, I/O flag values,

and compare accumulator

STKY

Sticky arithmetic status flags, circular buffer

overflow flags, stack status flags (not sticky)

USTAT1

User status register l

USTAT2

User status register 2

*read-only

Refer to User’s Manual for bit-level definitions of each register.

Table IV. ALU Compute Operations

Fixed-Point

Floating-Point

Rn = Rx + Ry

Fn = Fx + Fy

Rn = Rx – Ry

Fn = Fx – Fy

Rn = Rx + Ry, Rm = Rx – Ry

Fn = Fx + Fy, Fm = Fx – Fy

Rn = Rx + Ry + CI

Fn = ABS (Fx + Fy)

Rn = Rx – Ry + CI – l

Fn = ABS (Fx – Fy)

Rn = (Rx + Ry)/2

Fn = (Fx + Fy)/2

COMP(Rx, Ry)

COMP(Fx, Fy)

Rn = –Rx

Fn = –Fx

Rn = ABS Rx

Fn = ABS Fx

Rn = PASS Rx

Fn = PASS Fx

Rn = MIN(Rx, Ry)

Fn = MIN(Fx, Fy)

Rn = MAX(Rx, Ry)

Fn = MAX(Fx, Fy)

Rn = CLIP Rx BY Ry

Fn = CLIP Fx BY Fy

Rn = Rx + CI

Fn = RND Fx

Rn = Rx + CI – 1

Fn = SCALB Fx BY Ry

Rn = Rx + l

Rn = MANT Fx

Rn = Rx – l

Rn = LOGB Fx

Rn = Rx AND Ry

Rn = FIX Fx BY Ry

Rn = Rx OR Ry

Rn = FIX Fx

Rn = Rx XOR Ry

Fn = FLOAT Rx BY Ry

Rn = NOT Rx

Fn = FLOAT Rx

Fn = RECIPS Fx

Fn = RSQRTS Fx

Fn = Fx COPYSIGN Fy

Rn, Rx, Ry R15–R0; register file location, fixed-point

Fn, Fx, Fy F15–F0; register file location, floating point