Pin descriptions, Basic system configuration, Rev. c –5 – Analog Devices ADSP-21020 User Manual

Page 5: Pin name type function pma

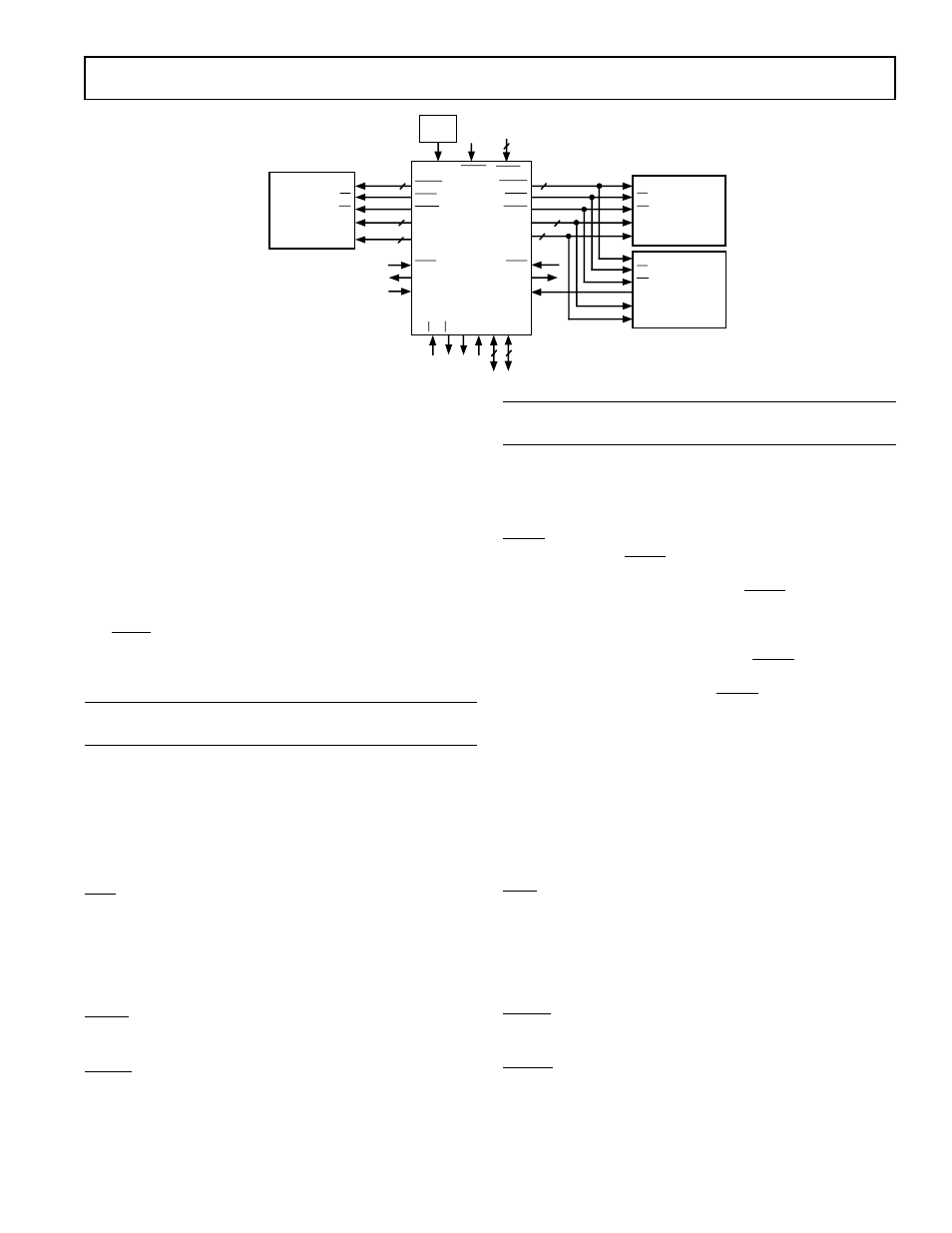

ADSP-21020

REV. C

–5–

4

1

×

CLOCK

CLKIN

PMA

PMD

DMACK

DMA

DMD

ADSP-21010

24

48

32

32

2

PMACK

4

DMPAGE

PMPAGE

FLAG3-0

JTAG

5

4

RCOMP

TIMEXP

ADDR

DATA

PROGRAM

MEMORY

SELECTS

OE

WE

PMS1-0

PMRD

PMWR

DMRD

DMWR

DMTS

DATA

MEMORY

ACK

PERIPHERALS

ADDR

DATA

ADDR

DATA

SELECTS

SELECTS

OE

WE

OE

WE

BR

BG

RESET

IRQ3-0

PMTS

DMS3-0

Figure 2. Basic System Configuration

The ADSP-21020 also implements on-chip emulation through

the JTAG test access port. The processor’s eight sets of break-

point range registers enable program execution at full speed

until reaching a desired break-point address range. The

processor can then halt and allow reading/writing of all the

processor’s internal registers and external memories through the

JTAG port.

PIN DESCRIPTIONS

This section describes the pins of the ADSP-21020. When

groups of pins are identified with subscripts, e.g. PMD

47–0

, the

highest numbered pin is the MSB (in this case, PMD

47

). Inputs

identified as synchronous (S) must meet timing requirements

with respect to CLKIN (or with respect to TCK for TMS, TDI,

and TRST). Those that are asynchronous (A) can be asserted

asynchronously to CLKIN.

O = Output; I = Input; S = Synchronous; A = Asynchronous;

P = Power Supply; G = Ground.

Pin

Name

Type

Function

PMA

23–0

O

Program Memory Address. The ADSP-21020

outputs an address in program memory on

these pins.

PMD

47–0

I/O

Program Memory Data. The ADSP-21020

inputs and outputs data and instructions on

these pins. 32-bit fixed-point data and 32-bit

single-precision floating-point data is trans-

ferred over bits 47-16 of the PMD bus.

PMS

1–0

O

Program Memory Select lines. These pins are

asserted as chip selects for the corresponding

banks of program memory. Memory banks

must be defined in the memory control

registers. These pins are decoded program

memory address lines and provide an early

indication of a possible bus cycle.

PMRD

O

Program Memory Read strobe. This pin is

asserted when the ADSP-21020 reads from

program memory.

PMWR

O

Program Memory Write strobe. This pin is

asserted when the ADSP-21020 writes to

program memory.

PMACK I/S

Program Memory Acknowledge. An external

device deasserts this input to add wait states

to a memory access.

Pin

Name

Type

Function

PMPAGE O

Program Memory Page Boundary. The

ADSP-21020 asserts this pin to signal that a

program memory page boundary has been

crossed. Memory pages must be defined in

the memory control registers.

PMTS

I/S

Program Memory Three-State Control.

PMTS

places the program memory address,

data, selects, and strobes in a high-

impedance state. If PMTS is asserted while

a PM access is occurring, the processor will

halt and the memory access will not be

completed. PMACK must be asserted for at

least one cycle when PMTS is deasserted to

allow any pending memory access to com-

plete properly. PMTS should only be

asserted (low) during an active memory

access cycle.

DMA

31–0

O

Data Memory Address. The ADSP-21020

outputs an address in data memory on these

pins.

DMD

39–0

I/O

Data Memory Data. The ADSP-21020

inputs and outputs data on these pins.

32-bit fixed point data and 32-bit

single-precision floating point data is

transferred over bits 39-8 of the DMD bus.

DMS

3–0

O

Data Memory Select lines. These pins are

asserted as chip selects for the correspon-

ding banks of data memory. Memory banks

must be defined in the memory control

registers. These pins are decoded data

memory address lines and provide an early

indication of a possible bus cycle.

DMRD

O

Data Memory Read strobe. This pin is

asserted when the ADSP-21020 reads from

data memory.

DMWR

O

Data Memory Write strobe. This pin is

asserted when the ADSP-21020 writes to

data memory.

DMACK

I/S

Data Memory Acknowledge. An external

device deasserts this input to add wait states

to a memory access.