Immediate move instructions, Miscellaneous instructions – Analog Devices ADSP-21020 User Manual

Page 8

ADSP-21020

REV. C

–8–

Table II. Condition and Termination Codes

Name

Description

eq

ALU equal to zero

ne

ALU not equal to zero

ge

ALU greater than or equal to zero

lt

ALU less than zero

le

ALU less than or equal to zero

gt

ALU greater than zero

ac

ALU carry

not ac

Not ALU carry

av

ALU overflow

not av

Not ALU overflow

mv

Multiplier overflow

not mv

Not multiplier overflow

ms

Multiplier sign

not ms

Not multiplier sign

sv

Shifter overflow

not sv

Not shifter overflow

sz

Shifter zero

not sz

Not shifter zero

flag0_in

Flag 0

not flag0_in

Not Flag 0

flag1_in

Flag 1

not flag1_in

Not Flag l

flag2_in

Flag 2

not flag2_in

Not Flag 2

flag3_in

Flag 3

not flag3_in

Not Flag 3

tf

Bit test flag

not tf

Not bit test flag

lce

Loop counter expired (DO UNTIL)

not lce

Loop counter not expired (IF)

forever

Always False (DO UNTIL)

true

Always True (IF)

In a conditional instruction, the execution of the entire instruction is based on

the specified condition.

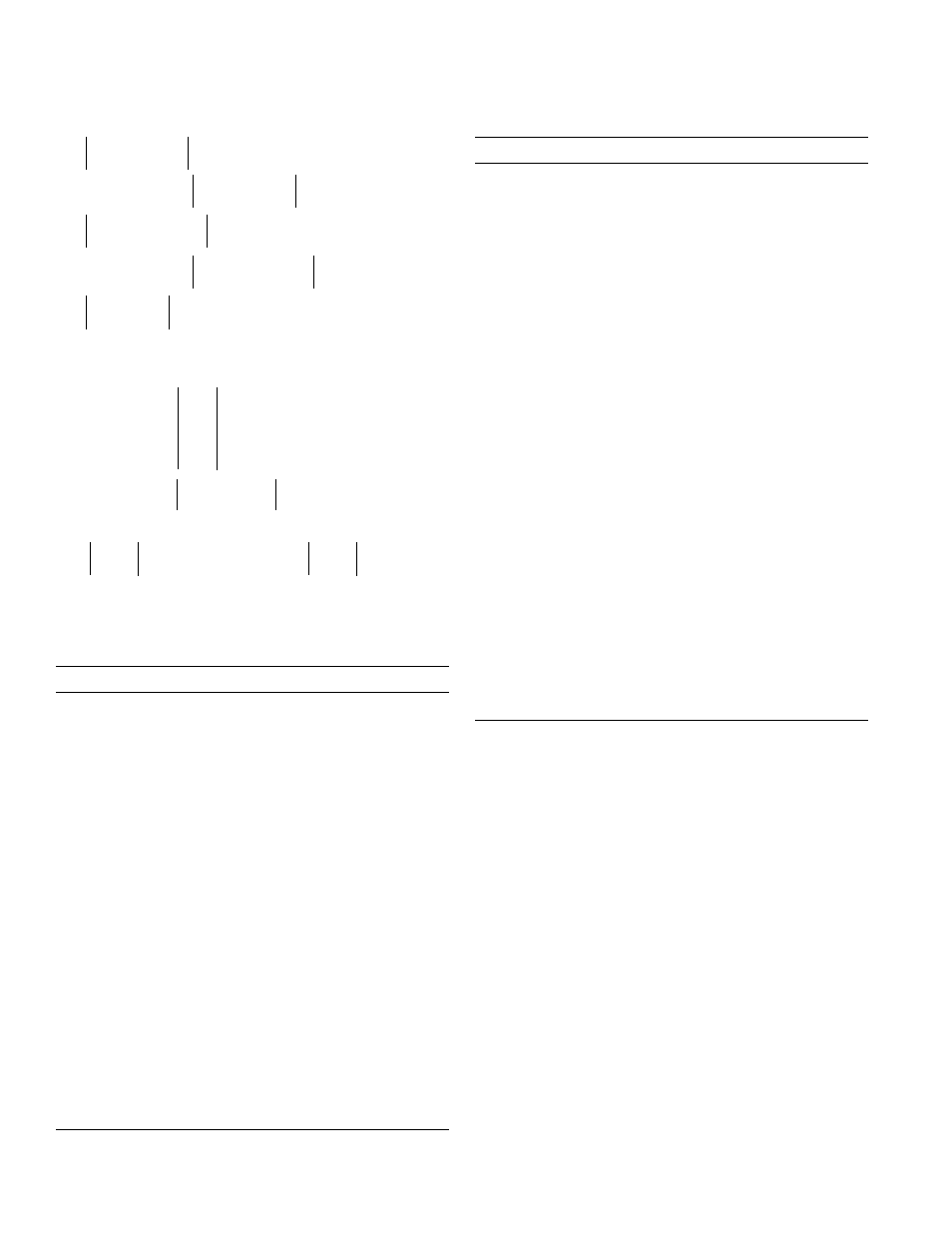

IMMEDIATE MOVE INSTRUCTIONS

14a. DM(

= ureg

;

PM(

14b. ureg =

DM(

;

PM(

15a. DM(

= ureg;

PM(< data24>, Ic)

15b. ureg =

DM(

;

PM(

16.

DM(Ia, Mb)

=

PM(Ic, Md)

17.

ureg =

MISCELLANEOUS INSTRUCTIONS

18. BIT

SET

sreg

CLR

TGL

TST

XOR

19a. MODIFY

(Ia,

|

;

(Ic,

|

19b. BITREV

(Ia,

;

20.

|

PUSH

LOOP

,

PUSH

STS ;

|

POP

POP

21. NOP ;

22. IDLE ;

Table I. Syntax Notation Conventions

Notation

Meaning

UPPERCASE

Explicit syntax—assembler keyword (nota-

tion only; assembler is not case-sensitive

and lowercase is the preferred programming

convention)

;

Instruction terminator

,

Separates parallel operations in an

instruction

italics

Optional part of instruction

| between lines |

List of options (choose one)

n-bit immediate data value

n-bit immediate address value

n-bit immediate PC-relative address value

compute

ALU, multiplier, shifter or multifunction

operation (from Tables IV-VII)

shiftimm

Shifter immediate operation

(from Table VI)

condition

Status condition (from Table II)

termination

Termination condition (from Table II)

ureg

Universal register (from Table III)

sreg

System register (from Table III)

dreg

R15-R0, F15-F0; register file location

Ia

I7-I0; DAG1 index register

Mb

M7-M0; DAG1 modify register

Ic

I15-I8; DAG2 index register

Md

M15-M8; DAG2 modify register