11-1 cpu feature, 11-2 dram configuration – AMD Socket AM2+ Quad Core Processor 790GX User Manual

Page 41

36

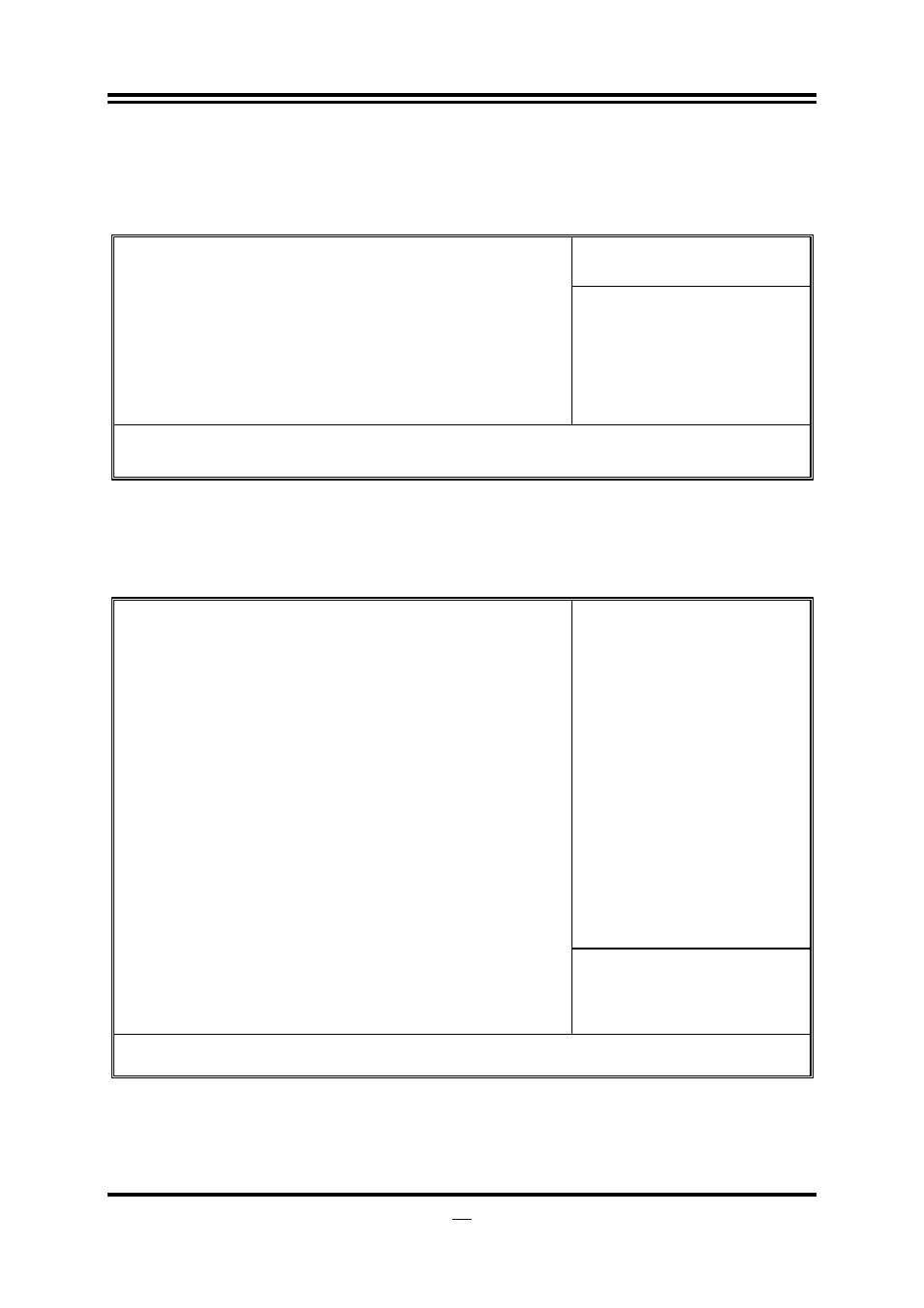

3-11-1 CPU

Feature

Phoenix – AwardBIOS CMOS Setup Utility

CPU Feature

Item Help

Virtualization Enabled

AMD K8 Cool & Quiet control Disabled

TLB Check Enabled

Advanced clock calibration Disabled

Value (ALL Cores) 2%

Value (Cores 0) 2%

Value (Cores 1) 2%

Value (Cores 2) 2%

Value (Cores 3) 2%

Menu Level >

↑↓→← Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Fail-safe Defaults F7:Optimized Defaults

3-11-2 DRAM

Configuration

Phoenix – AwardBIOS CMOS Setup Utility

DRAM Configuration

Item Help

DRAM Latency(tcl) Auto

(Trcd)RAS to CAS R/W Delay 6 Clocks

(Trp) Row precharge Time 6 Clocks

(Tras)Minimum RAS Active Time 18 bus clocks

DRAM Command Rate 2T

CKE base Power dowe mode Enabled

CKE BASED Powerdown per channel

Memclock tri-slating Disabled

Memory Hole Remapping Enabled

Auto optimize Bottom IO Enabled

*Bottom of

【31:24】IO space DO

Bottom of UMA DDRAM [31:24] FC

DDRII Timing Item Disabled

Refresh Mode Select Auto

Idle cycle limit Auto

TwTr Command Delay 3 bus clocks

Trfc 0 for DIMM0 75ns

* Trfc 1 for DIMM 1 75ns

* Trfc 2 for DIMM 2 75ns

* Trfc 3 for DIMM 3 75ns

* (Twr) write Recovery Time 6 bus clock

* (Trtp) Precharge Time 3 clocks

(Trc) Row cycle Time 26 bus clocks

Trc RAS to RAS Delay 5 clocks

Trcd RAS to CAS R/W Delay 6 clocks

Menu Level >>

↑↓→← Move Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Optimized Defaults F7:Standard Defaults

CAS # Latency

When synchronous DRAM is installed, the number of clock cycles of CAS latency depends

on the DRAM timing. The settings are: Auto,3, 4 and 5.

RAS-to-CAS Delay