2 floating-point registers, 1 register banks, Floating-point registers -5 – ARM VERSION 1.2 User Manual

Page 243

Vector Floating-point Programming

ARM DUI 0068B

Copyright © 2000, 2001 ARM Limited. All rights reserved.

6-5

6.2

Floating-point registers

The Vector Floating-point coprocessor has 32 single-precision registers, s0 to s31. Each

register can contain either a single-precision floating-point value, or a 32-bit integer.

These 32 registers are also treated as 16 double-precision registers, d0 to d15.

dn

occupies the same hardware as

s(2n)

and

s(2n+1)

.

You can use:

•

some registers for single-precision values at the same time as you are using others

for double-precision values

•

the same registers for single-precision values and double-precision values at

different times.

Do not attempt to use corresponding single-precision and double-precision registers at

the same time. No damage is caused but the results are meaningless.

6.2.1

Register banks

The VFP registers are arranged as four banks of:

•

eight single-precision registers, s0 to s7, s8 to s15, s16 to s23, and s24 to s31

•

four double-precision registers, d0 to d3, d4 to d7, d8 to d11, and d12 to d15

•

any combination of single-precision and double-precision registers.

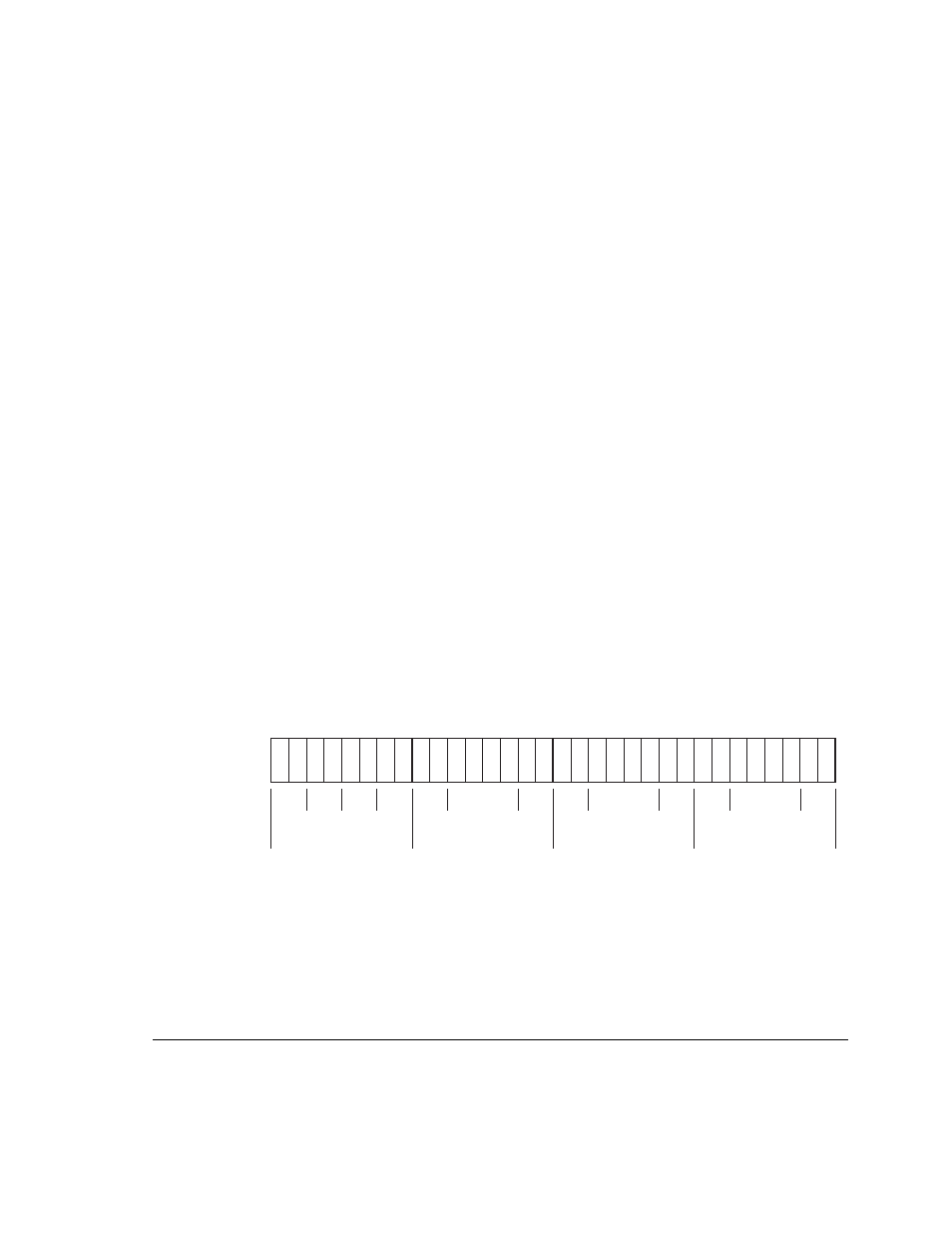

See Figure 6-1 for further clarification.

Figure 6-1 VFP register banks

Bank 0

Bank 1

Bank 2

Bank 3

d0

d1

d3

d4

d7

d8

d11 d12

d15

d2

...

...

...

s0 s1

s7 s8

s15 s16

s23 s24

s31

s2 s3 s4 s5 s6

...

...

...