Rext (external timing resistor), Sensor drive and measurement pins, 4 spi timing requirements – PNI RM3000-F Sensor Suite User Manual

Page 27: Spi timing requirements, Figure 4-4: spi timing diagram

PNI Sensor Corporation

Doc #1016102 r04

RM3000-f & RM2000-f Sensor Suite User Manual

Page 27

R

EXT

(External Timing Resistor)

R

EXT

ties to the external timing resistor for the high-speed clock. The recommended

value for the resistor and associated clock speed are defined in Table 3-1.

Sensor Drive and Measurement Pins

The various sensor drive and measurement pins should be connected to the sensors.

For a north-east-down (NED) reference frame, the connections should be as defined

4.4 SPI Timing Requirements

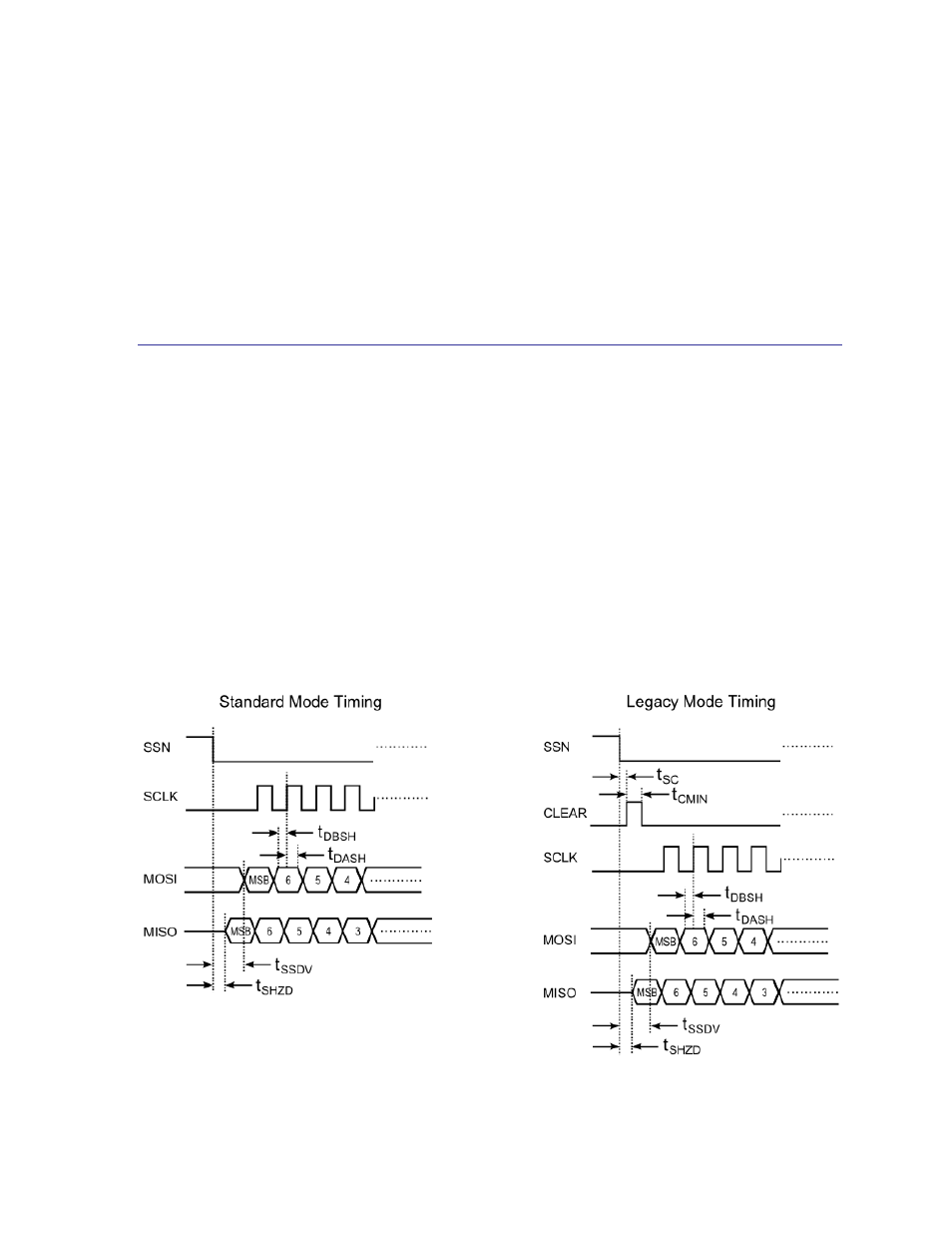

When implementing a SPI port, whether a dedicated hardware peripheral port or a software-

implemented port using general purpose I/O (also known as Bit-Banging), the timing

parameters, defined in Figure 4-4 and specified in Table 4-2, must be met to ensure reliable

communication. Note that Standard Mode and Legacy Mode timing requirements are

identical with the exception of Legacy Mode utilizing the CLEAR line. The SPI clock

(SCLK) should run at 1 MHz or less. Generally data is considered valid while SCLK is

HIGH, and data is in transition when SCLK is LOW. The clock polarity used with the 3D

MagIC is zero (exclusively CPOL=0). Data is present on MISO or should be presented on

MOSI before the first low to high clock transition (exclusively CPHA = 0).

Figure 4-4: SPI Timing Diagram