Input interface, Fading simulation – Atec Rohde-Schwarz-SFQ Series User Manual

Page 10

10

TV Test Transmitter R&S

®

SFQ

All interleaver modes defined in J.83-B

are implemented (level 1 and level 2),

allowing the system to adapt easily to dif-

ferent transmission conditions.

FEC frame: With 64QAM, a frame sync

trailer is inserted after 60 Reed-Solomon

packets (with 256QAM after 88 Reed-

Solomon packets), thus forming an FEC

frame. The frame sync trailer is a sync

word that carries information about the

current interleaver configuration. The

trailer is inserted immediately ahead of

trellis coding and used by the receiver for

FEC synchronization and interleaver

mode evaluation.

The trellis coder for 64QAM performs dif-

ferential coding of the input data as well

as 4/5 punctured convolutional coding.

The overall code rate is 14/15, i.e. the trel-

lis coder generates 15 output bits from 14

input bits. The output word length of the

trellis coder is 6 bits, corresponding to the

modulation level of 6 for 64QAM. The out-

put signal of the trellis coder is applied to

the mapper, which converts the symbols

formed by the trellis coder into constella-

tion points. The trailer is also coded by the

trellis coder like normal FEC data and,

because of its length, occupies all the bit

positions in a trellis group.

The differential/convolutional encoder in

the trellis block for 256QAM is identical to

the 64QAM trellis coder but has an overall

code rate of 19/20. In contrast to 64QAM,

the trailer is inserted only at the differen-

tially coded bit positions of a trellis group

and transmitted in five sync trellis groups

because of its length. The output word

length is 8 bits, corresponding to 256 con-

stellation points.

After the mapper and prior to modulation,

the output spectrum is band-limited by a

√cos roll-off filter to match the 6 MHz

channel spacing. Roll-off is 0.18 with

64QAM and 0.12 with 256QAM in line

with the standard.

Input interface

The optional input interface adds two fur-

ther inputs to the base units TS PARALLEL

input in LVDS (low voltage differential sig-

nalling) format: SPI (synchronous parallel

interface) and ASI (asynchronous serial

interface). An SMPTE310M input is more-

over available in the case of ATSC/8VSB

and J.83-B.

SPI and ASI inputs allow setting of the

symbol rate independently of the input

data rate, so that the input data rate is

independent of the symbol rate or chan-

nel bandwidth. To this effect, all null

packets are removed. The data rate

required for a given symbol rate or band-

width is obtained by stuffing, i.e. by

inserting new null packets. The PCR (pro-

gram clock reference) values are adapted.

A built-in synthesizer ensures an accurate

data clock at all inputs. For synchroniza-

tion to a receiver, an external clock can be

applied to ASI and SPI instead of the

internal clock.

Fading simulation

For receiver testing, it is necessary to sim-

ulate all real-life transmission conditions

as completely as possible and in a repro-

ducible way. The R&S SFQ caters for this

necessity by offering a fading simulator in

addition to the noise generator. The fad-

ing simulator is indispensable for the sim-

ulation of terrestrial

− and in particular

mobile

− receive conditions, but can also

be used for QAM and QPSK (max. 14 MHz

RF bandwidth), for example to simulate

reflection. For fading simulation, a signal

is passed through 6 or 12 parallel paths

which are combined again ahead of the

modulator. Each active simulation path

shapes the signal independently of the

other paths and without any synchroniza-

tion between the paths.

For each path, loss and delay can be set

individually and a profile selected. Vari-

ous profiles are available. The constant

phase profile allows extremely short

delays to be simulated.

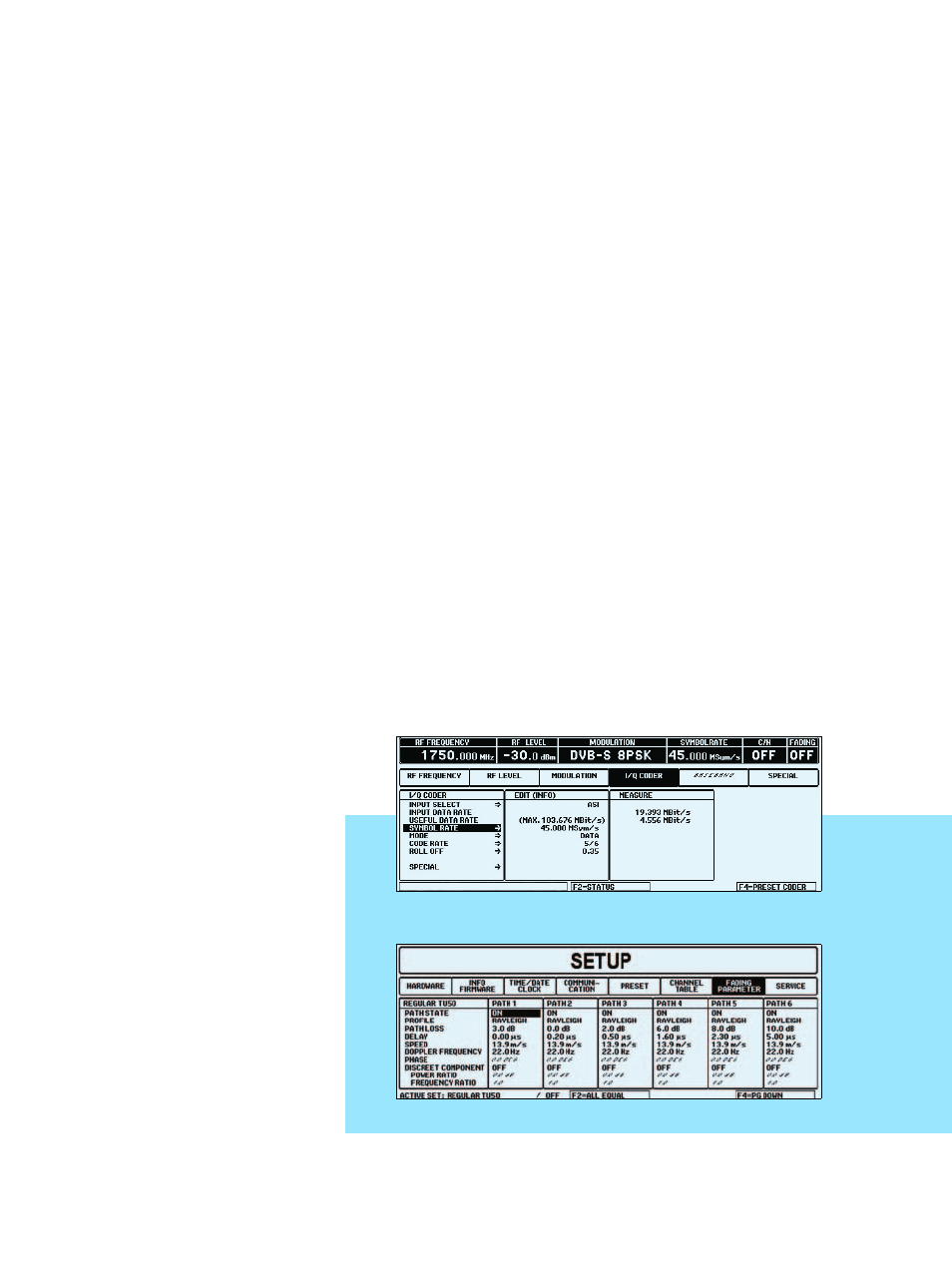

Typical operating menu

Setup menu for fading: regular TU50 (i.e. typical urban, 50 km/h, 6 paths)