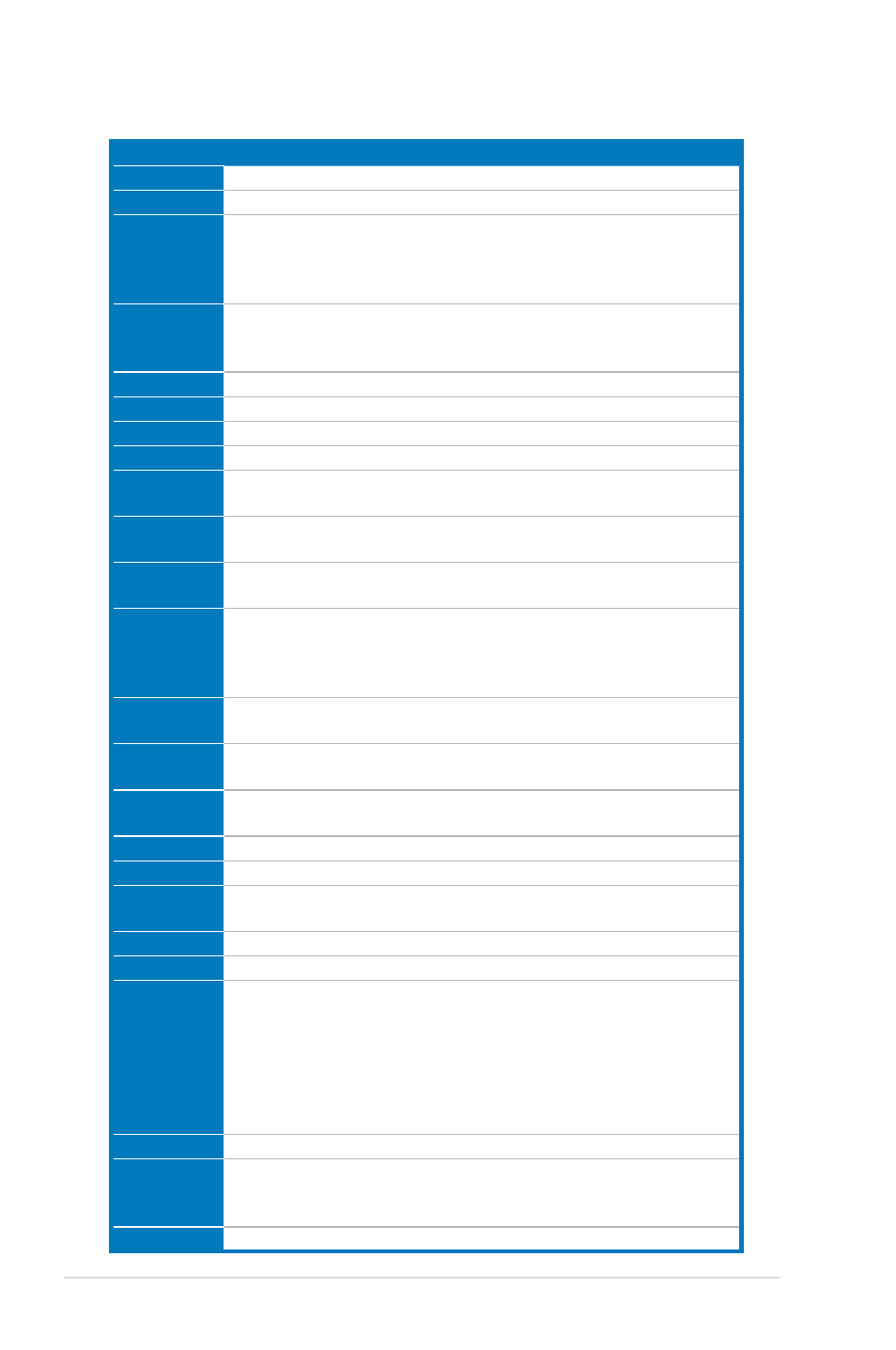

A.4 debug code table – Asus Maximus Extreme User Manual

Page 194

A-4

Appendix: CPU features

Code

Description

CPU INIT

CPU Initiation

DET CPU

Test CMOS R/W functionality.

CHIPINIT

Early chipset initialization:

-Disable shadow RAM

-Disable L2 cache

-Program basic chipset registers

DET DRAM

Detect memory

-Auto-detection of DRAM size, type and ECC.

-Auto-detection of L2 cache

DC FCODE

Expand compressed BIOS code to DRAM

EFSHADOW

Call chipset hook to copy BIOS back to E000 & F000 shadow RAM.

INIT IO

Initialize IO devices.

INIT HWM

Initialize Hardware Monitor.

CLR SCRN

1. Blank out screen

2. Clear CMOS error flag

INIT8042

1. Clear 8042 interface

2. Initialize 8042 self-test

ENABLEKB

1. Test special keyboard controller for Super I/O chips.

2. Enable keyboard interface.

DIS MS

1. Disable PS/2 mouse interface (optional).

2. Auto detect ports for keyboard & mouse followed by a port &

interface swap (optional).

3. Reset keyboard for Super I/O chips.

R/W FSEG

Test F000h segment shadow to see whether it is R/W-able or not. If

test fails, keep beeping the speaker.

DET FLASH

Auto detect flash type to load appropriate flash R/W codes into the run

time area in F000 for ESCD & DMI support.

TESTCMOS

Use walking 1’s algorithm to check out interface in CMOS circuitry.

Also set real-time clock power status, and then check for override.

PRG CHIP

Program chipset default values into chipset.

INIT CLK

Initialize clock generator.

CHECKCPU

Detect CPU information including brand, type and CPU level (586 or

686).

INTRINIT

Initial interrupts vector table.

INITINT9

Initialize INT 09 buffer

CPUSPEED

1. Program CPU internal MTRR (Pentium class CPU) for 0-640K

memory address.

2. Initialize the APIC for Pentium class CPU.

3. Program early chipset according to CMOS setup. Example: onboard

IDE controller.

4. Measure CPU speed.

5. Invoke video BIOS.

VGA BIOS

Initialize VGA BIOS

TESTVRAM

1. Initialize multi-language

2. Put information on screen display, including BIOS logo, CPU type,

CPU speed .

RESET KB

Reset keyboard.

A.4

Debug code table