Detailed description, Pin description – Rainbow Electronics MAX111 User Manual

Page 9

MAX110/MAX111

Low-Cost, 2-Channel, ±14-Bit Serial ADCs

_______________________________________________________________________________________

9

_______________Detailed Description

The MAX110/MAX111 ADC converts low-frequency

analog signals to a 16-bit serial digital output (14 data

bits, a sign bit, and an overrange bit) using a first-order

sigma-delta loop (Figure 1). The differential input volt-

age is internally connected to a precision voltage-to-

current converter. The resulting current is integrated

and applied to a comparator. The comparator output

then drives an up/down counter and a 1-bit DAC. When

the DAC output is fed back to the integrator input, the

sigma-delta loop is completed.

During a conversion, the comparator output is a V

REF-

to V

REF+

square wave; its duty cycle is proportional to

the magnitude of the differential input voltage applied

to the ADC. The up/down counter clocks data in from

the comparator at the oversampling clock rate and

averages the pulse-width-modulated (PWM) square

wave to produce the conversion result. A 16-bit static

shift register stores the result at the end of the conver-

sion. Figure 2 shows the ADC waveforms for a differen-

tial analog input equal to 1/2 (V

REF+

- V

REF-

). The

resulting comparator and 1-bit DAC outputs are high

for seven cycles and low for three cycles of the over-

sampling clock.

Since the analog input signal is integrated over many

clock cycles, much of the signal and quantization noise

is attenuated. The more clock cycles allowed during

each conversion, the greater the noise attenuation (see

Programming Conversion Time

).

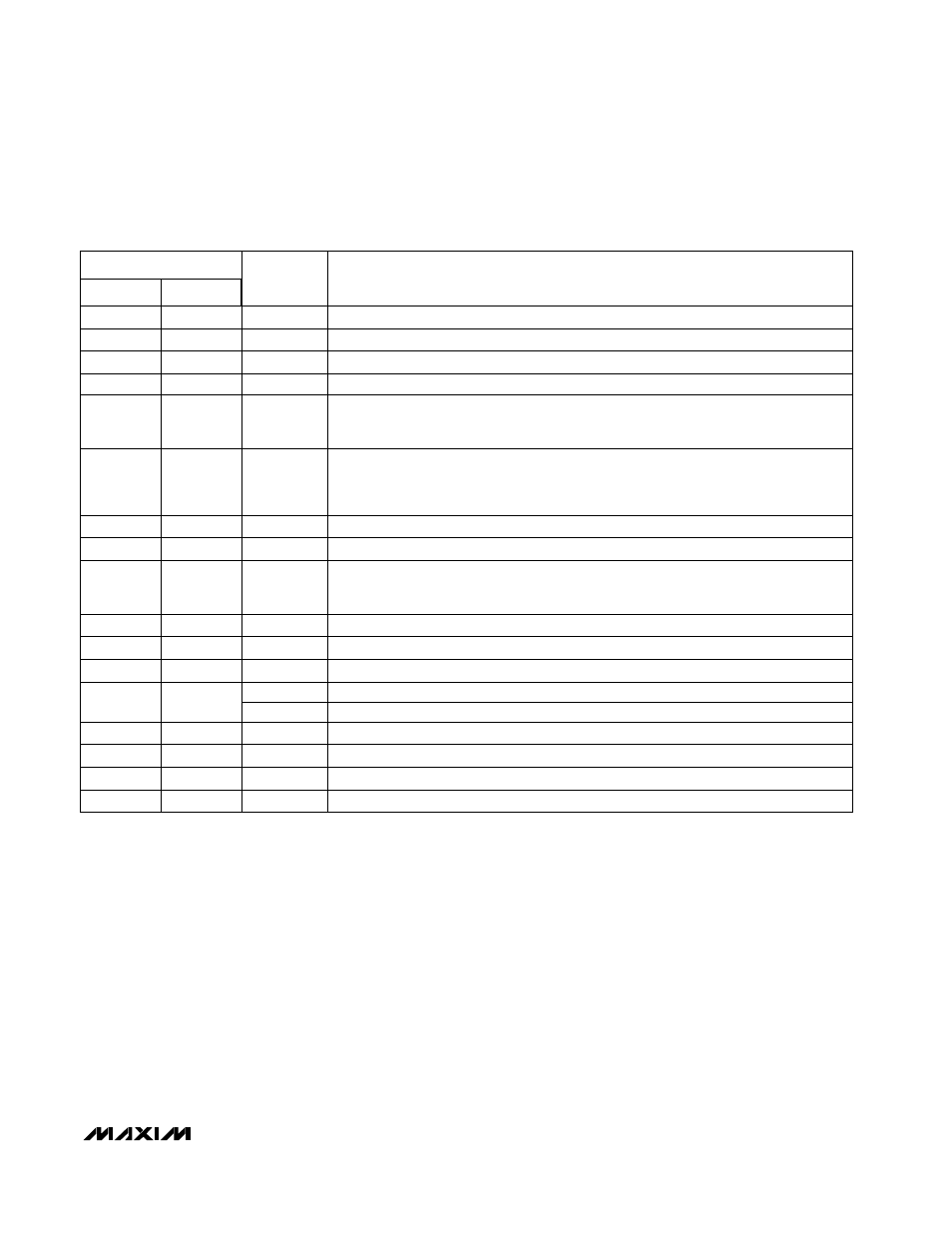

______________________________________________________________Pin Description

Clock Input / RC Oscillator Output. TTL/CMOS-compatible oversampling clock input

when RCSEL = GND. Connects to the internal RC oscillator when RCSEL = V

DD

. XCLK

must be connected to V

DD

or GND through a resistor (1M

Ω

or less) when RC OSC

mode is selected.

XCLK

8

Serial Clock Input. TTL/CMOS-compatible clock input for serial-interface data I/O.

SCLK

9

Busy Output. Goes low at conversion start, and returns high at end of conversion.

BUSY

10

Positive Power-Supply Input—connect to +5V

V

DD

6

RC Select Input. Connect to GND to select external clock mode. Connect to V

DD

to

select RC OSC mode. XCLK must be connected to V

DD

or GND through a resistor

(1M

Ω

or less) when RC OSC mode is selected.

RCSEL

7

Positive Reference Input

REF+

3

Negative Reference Input

REF-

2

Channel 1 Positive Analog Input

IN1+

1

FUNCTION

NAME

SSOP

6

7

8

4

5

3

2

PIN

1

DIP/SO

Chip-Select Input. Pull this input low to perform a control-word-write/data-read opera-

tion. A conversion begins when CS returns high, provided NO-OP is a 1. See the sec-

tion

Using the MAX110/MAX111 with SPI, QSPI, and MICROWIRE Serial Interfaces.

CS

11

9

Serial Data Output. High-impedance when CS is high.

DOUT

12

10

Serial Data Input. See

Control Register

section.

DIN

13

11

Digital Ground

GND

16

12

MAX110 Negative Power-Supply Input—connect to -5V

V

SS

Channel 2 Negative Analog Input

IN2-

18

14

Channel 2 Positive Analog Input

IN2+

19

15

Channel 1 Negative Analog Input

IN1-

20

16

No Connect—there is no internal connection to this pin

N.C.

4, 5, 14, 15

—

MAX111 Analog Ground

AGND

17

13