Rainbow Electronics MAX111 User Manual

Page 18

MAX110/MAX111

Low-Cost, 2-Channel, ±14-Bit Serial ADCs

18

______________________________________________________________________________________

Selecting the Oversampling

Clock Frequency

Choose the oversampling frequency, f

OSC

, carefully to

achieve the best relative-accuracy performance from the

MAX110/MAX111 (see

Typical Operating Characteristics

).

Clock Divider-Ratio Control Bits

Bits 7 and 8 (DV2 and DV4) program the clock-

frequency divider network. The divider network sets the

frequency ratio between f

XCLK

(the frequency of the

external TTL/CMOS clock or internal RC oscillator) and

f

OSC

(the oversampling frequency used by the ADC).

An oversampling clock frequency between 450kHz and

700kHz is optimum for the converter.

Best perfor-

mance over the extended temperature range is

obtained by choosing 1MHz or 1.024MHz with the

divide-by-2 option (DV2 = 1) (see the section

Effect

of Dither on INL

)

. To determine the converter’s accura-

cy at other clock frequencies, see the

Typical

Operating Characteristics

and Table 5.

Effect of Dither on Relative Accuracy

First-order sigma-delta converters require dither for

randomizing any systematic tone being generated in

the modulator. The frequency of the dither source plays

an important role in linearizing the modulator. The ratio

of the dither generator’s frequency to that of the modu-

lator’s oversampling clock can be changed by setting

the DV2/DV4 bits. The XCLK clock is directly used by

the dither generator while the DV2/DV4 bits reduce the

oversampling clock by a ratio of 2 or 4. Over the com-

mercial temperature range, any ratio (i.e., 1, 2, or 4)

between the dither frequency and the oversampling

clock frequency can be used for best performance.

Over the extended and military temperature ranges, the

ratio of 2 or 4 gives the best performance. See the

Typical Operating Characteristics

to observe the effect

of the clock divider on the converter’s linearity.

50Hz/60Hz Line Frequency Rejection

High rejection of 50Hz or 60Hz is obtained by using an

oversampling clock frequency and a clock-cycles/con-

version setting so the conversion time equals an inte-

gral number of line cycles, as in the following equation:

f

OSC

= f

LINE

x m / n

where f

OSC

is the oversampling clock frequency, f

LINE

= 50Hz or 60Hz, m is the number of clock cycles per

conversion (see Table 4), and n is the number of line

cycles averaged every conversion.

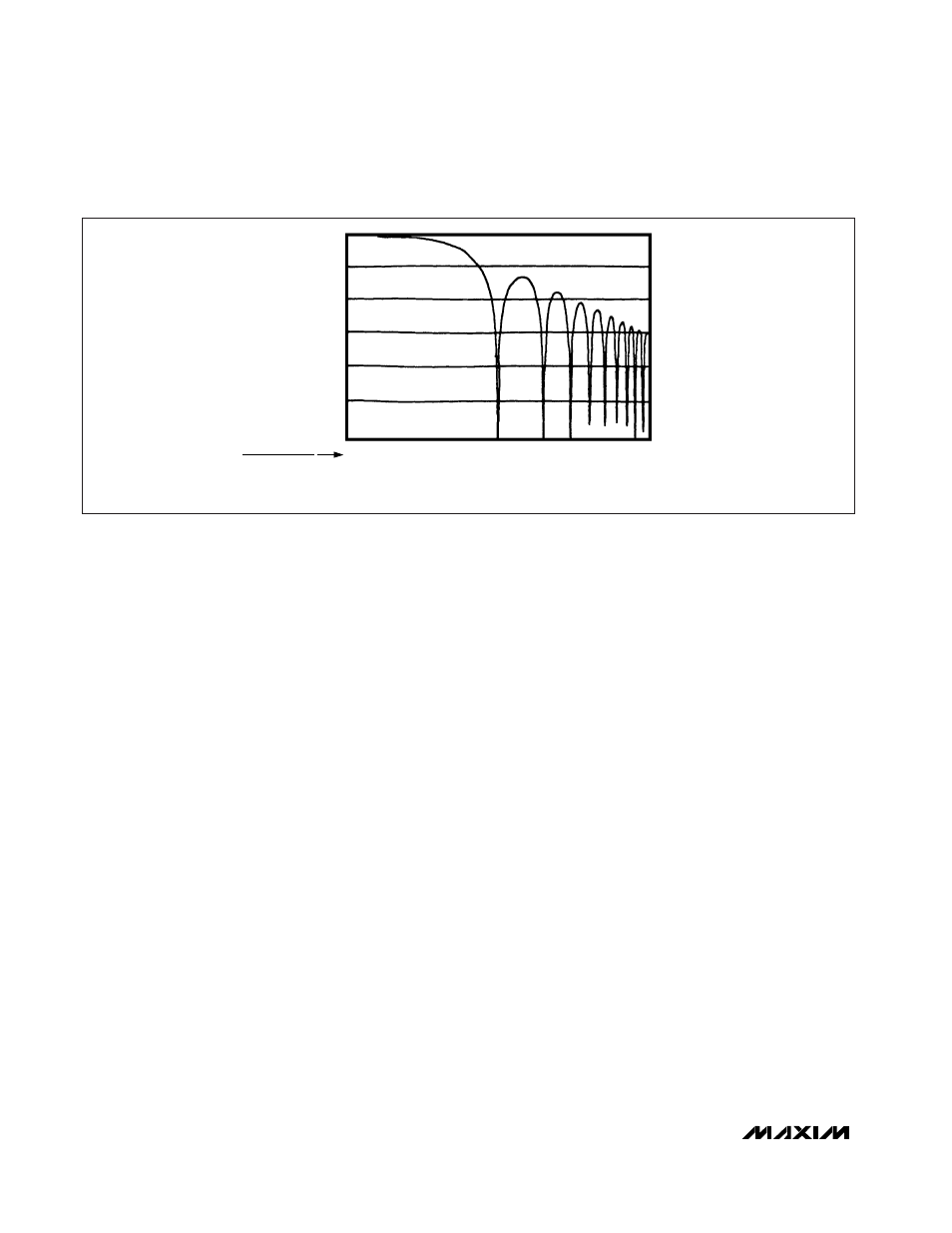

This noise rejection is inherent in integrating and

sigma-delta ADCs, and follows a SIN(X) / X function

(Figure 9). Notches in this function represent extremely

high rejection, and correspond to frequencies with an

integral number of cycles in the MAX110/MAX111’s

selected conversion time.

The shortest conversion time resulting in maximum

simultaneous rejection of both 60Hz and 50Hz line fre-

quencies is 100ms. When using the MAX111, use a

200ms conversion time for maximum 60Hz and 50Hz

rejection

and

optimum performance. For either device,

select the appropriate oversampling clock frequency

and either an 81,240 or 102,400 clock cycles per con-

version (CCPC) ratio. Table 6 suggests the possible

configurations.

0

-10

-20

-30

-40

-50

-60

0.1

1

CONVERSION TIME

LINE CYCLE PERIOD

SIGNAL FREQUENCY IN Hz

FOR 100ms CONVERSION

TIME (see Table 6)

1

10

20

30

40 50 60 70 80 90100

2

3

4

5 6 7 8 9 10

GAIN (dB)

Figure 9. MAX110/MAX111 Noise Rejection Follows SIN(X) / X Function