Rainbow Electronics MAX2062 User Manual

Page 21

______________________________________________________________________________________ 21

MAX2062

Dual 50MHz to 1000MHz High-Linearity,

Serial/Parallel-Controlled Analog/Digital VGA

Attenuator and DAC Operation

The two analog attenuators are controlled by an external

control voltage applied at A_VCTL_1 and A_VCTL_2

(pins 39 and 22) or by the on-chip 8-bit DACs, while

the digital attenuators are controlled through the SPI-

compatible interface or through two independent,

parallel 5-bit buses. The DAC enable/disable logic-input

pin (AA_SP) and digital attenuator SPI/parallel control

selection logic-input pin (DA_SP) determine how the

attenuators are controlled.

Digital Attenuator Settings

Using the Parallel Control Bus

To capitalize on its fast 25ns switching capability, the

device offers a supplemental 5-bit parallel control inter-

face. The digital logic attenuator control pins (D0_–D4_)

enable the attenuator stages (see Tables 3 and 4).

Direct access to these 5-bit buses enables the user to

avoid any programming delays associated with the SPI

interface. One of the limitations of any SPI bus is the

speed at which commands can be clocked into each

peripheral device. By offering direct access to the 5-bit

parallel interface, the user can quickly shift between

digital attenuator states needed for critical fast-attack

automatic gain control (AGC) applications.

Note that when the digital attenuators are controlled by

the SPI bus, the control voltages of each digital attenua-

tor appears on the five parallel control pins (pins 14–17

and 19 for digital attenuator 2, pins 42 and 44–47 for

digital attenuator 1). When the digital attenuators are

in SPI mode, the parallel control pins must be left

unconnected.

Rapid-Fire Preprogrammed

Attenuation States

The device has an added feature that provides rapid-

fire gain selection among four preprogrammed attenu-

ation steps. As with the supplemental 5-bit buses

previously mentioned, this rapid-fire gain selection allows

the user to quickly access any one of four customized

digital attenuation states without incurring the delays

associated with reprogramming the device through the

SPI bus.

The switching speed is comparable to that achieved

using the supplemental 5-bit parallel buses. However, by

employing this specific feature, the digital attenuator I/O

is further reduced by a factor of either 5 or 2.5 (5 control

bits vs. 1 or 2, respectively), depending on the number

of states desired.

The user can employ the STA_A_1 and STA_B_1

(STA_A_2 and STA_B_2 for digital attenuator 2) logic-

input pins to apply each step as required (see Tables

5 and 6). Toggling just the STA_A_1 pin (1 control bit)

yields two preprogrammed attenuation states; toggling

both the STA_A_1 and STA_B_1 pins together (2 control

bits) yields four preprogrammed attenuation states.

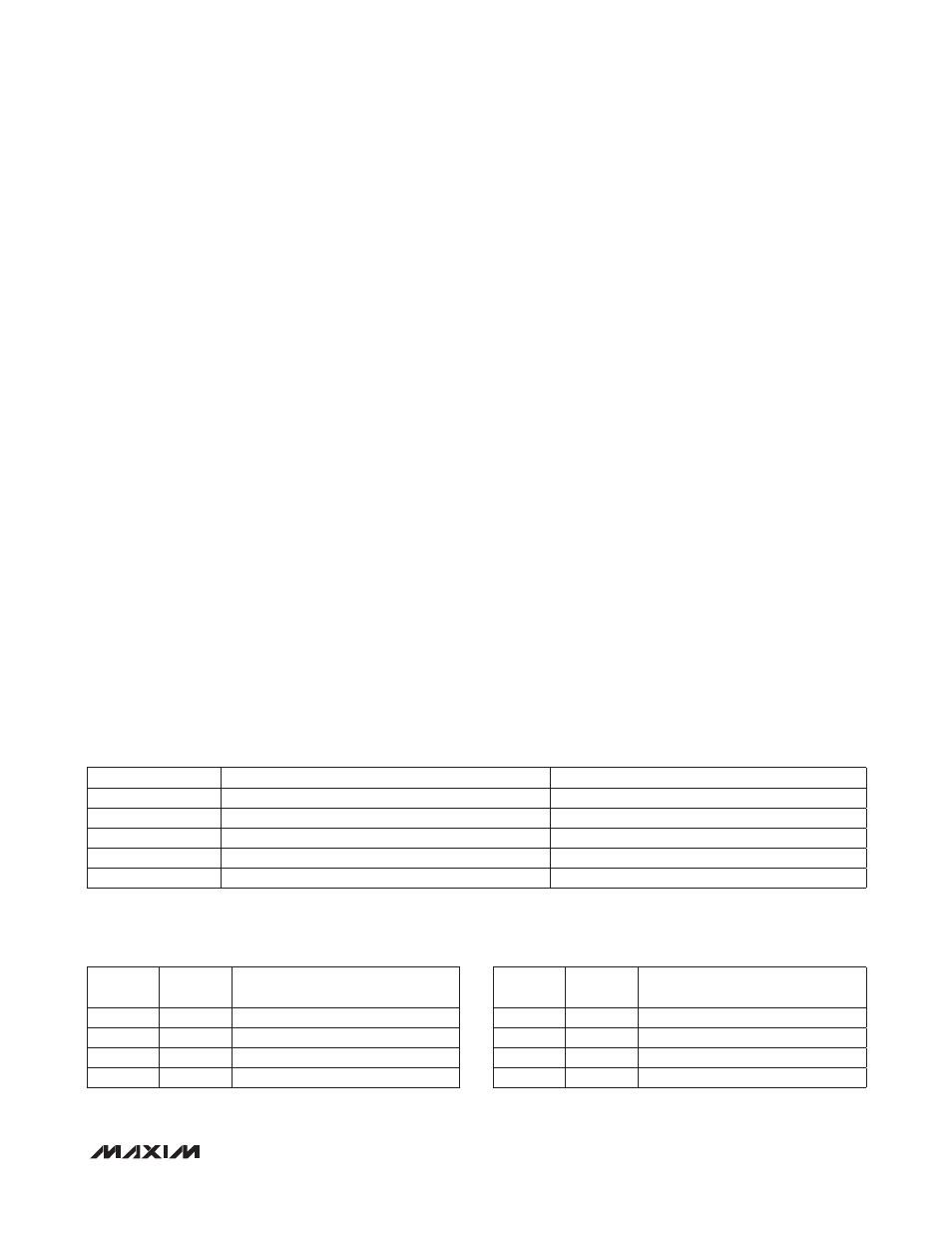

Table 4. Digital Attenuator Settings (Parallel Control, DA_SP = 0)

Table 5. Programmed Attenuation State

Settings for Attenuator 1 (DA_SP = 1)

Table 6. Programmed Attenuation State

Settings for Attenuator 2 (DA_SP = 1)

*Defined by SPI programming bits D8:D27 (see Table 3 for

details).

**Defined by SPI programming bits D36:D55 (see Table 3 for

details).

INPUT

LOGIC = 0 (OR GROUND)

LOGIC = 1

D0

Disable 1dB attenuator

Enable 1dB attenuator

D1

Disable 2dB attenuator

Enable 2dB attenuator

D2

Disable 4dB attenuator

Enable 4dB attenuator

D3

Disable 8dB attenuator

Enable 8dB attenuator

D4

Disable 16dB attenuator

Enable 16dB attenuator

STA_A_1 STA_B_1

SETTING FOR DIGITAL

ATTENUATOR 1*

0

0

Preprogrammed attenuation state 1

1

0

Preprogrammed attenuation state 2

0

1

Preprogrammed attenuation state 3

1

1

Preprogrammed attenuation state 4

STA_A_2 STA_B_2

SETTING FOR DIGITAL

ATTENUATOR 2**

0

0

Preprogrammed attenuation state 1

1

0

Preprogrammed attenuation state 2

0

1

Preprogrammed attenuation state 3

1

1

Preprogrammed attenuation state 4