Electrical characteristics (continued), Timing characteristics – Rainbow Electronics MAX194 User Manual

Page 4

MAX194

14-Bit, 85ksps ADC with 10µA Shutdown

4

_______________________________________________________________________________________

VDDD = VDDA = 5.25V, VSSD = VSSA = -5.25V

VDDD = VDDA = 5.25V, VSSD = VSSA = -5.25V,

BP/UP/SHDN = 0V

VDDD = VDDA = 5.25V, VSSD = VSSA = -5.25V,

BP/UP/SHDN = 0V

VDDD = VDDA = 5.25V, VSSD = VSSA = -5.25V,

BP/UP/SHDN = 0V

VDDD = VDDA = 5.25V, VSSD = VSSA = -5.25V,

BP/UP/SHDN = 0V

CONDITIONS

mW

80

Power Dissipation

µA

0.1

5

I

SSA

VSSA Shutdown Supply Current

µA

0.1

5

I

DDA

VDDA Shutdown Supply Current

µA

1.6

5

I

DDD

VDDD Shutdown Supply Current

(Note 5)

µA

0.1

5

I

SSD

VSSD Shutdown Supply Current

UNITS

MIN

TYP

MAX

SYMBOL

PARAMETER

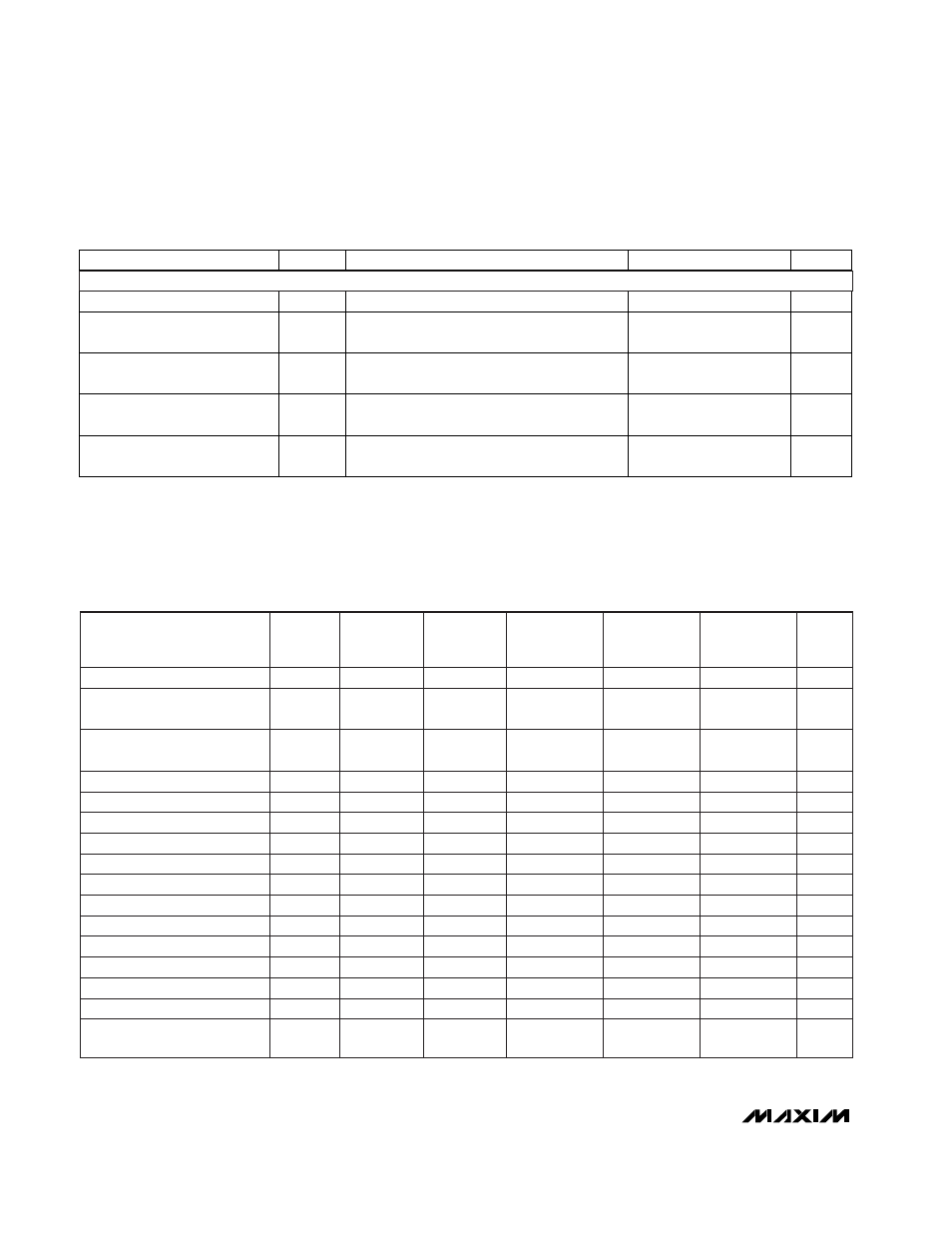

ELECTRICAL CHARACTERISTICS (continued)

(VDDD = VDDA = +5V, VSSD = VSSA = -5V, f

CLK

= 1.7MHz, V

REF

= +5V, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical

values are at T

A

= +25°C.)

TIMING CHARACTERISTICS

(VDDD = VDDA = +5V, VSSD = VSSA = -5V, unless otherwise noted.)

Note 1:

Accuracy and dynamic performance tests performed after calibration.

Note 2:

Tested with 50% duty cycle. Duty cycles from 25% to 75% at 1.7MHz are acceptable.

Note 3:

See

External Clock

section.

Note 4:

Guaranteed by design, not tested.

Note 5:

Measured in shutdown mode with CLK and SCLK low.

POWER REQUIREMENTS (cont.)

PARAMETER

SYMBOL CONDITIONS

T

A

= +25°C

TYP

T

A

= 0°C to

+70°C

MIN

MAX

T

A

= -40°C to

+85°C

MIN

MAX

T

A

= -55°C to

+125°C

MIN

MAX

UNITS

CONV Pulse Width

t

CW

20

30

35

ns

CONV to CLK Falling

Synchronization (Note 4)

t

CC1

10

10

10

ns

CONV to CLK Rising

Synchronization (Note 4)

t

CC2

40

40

ns

Data Access Time

t

DV

C

L

= 50pF

80

80

40

ns

Bus Relinquish Time

t

DH

C

L

= 10pF

40

40

40

ns

CLK to EOC High

t

CEH

C

L

= 50pF

300

300

350

ns

CLK to EOC Low

t

CEL

C

L

= 50pF

300

300

350

ns

CLK to DOUT Valid

t

CD

C

L

= 50pF

100

350

100

375

100

400

ns

SCLK to DOUT Valid

t

SD

C

L

= 50pF

20

140

20

160

20

160

ns

CS to SCLK Setup Time

t

CSS

75

75

75

ns

CS to SCLK Hold Time

t

CSH

-10

-10

-10

ns

Acquisition Time

t

AQ

2.4

2.4

2.4

µs

Calibration Time

t

CAL

14,000(

CLK

)

8.2

8.2

8.2

ms

RESET to CLK Setup Time

t

RCS

-40

-40

-40

ns

RESET to CLK Hold Time

t

RCH

120

120

120

Start-Up Time (Note 6)

t

SU

Exiting

shutdown

3.2

ns

90

µs

Note 6:

Settling time required after deasserting shutdown to achieve less than 0.1LSB additional error.