Rainbow Electronics MAX1401 User Manual

Page 17

MAX1401

+3V, 18-Bit, Low-Power, Multichannel,

Oversampling (Sigma-Delta) ADC

______________________________________________________________________________________

17

channels, selection of either calibration mode (01 or 10)

will cause the scanning sequence to be extended to

include a conversion on both the CALGAIN+/CALGAIN-

input pair and the CALOFF+/CALOFF- input pair. The

exact sequence depends on the state of the DIFF bit

(Table 4). When scanning, the calibration channels use

the PGA gain, format, and DAC settings defined by the

contents of Transfer Function Register 3.

BUFF:

(Default = 0) The BUFF bit controls operation of

the input buffer amplifiers. When this bit is 0, the inter-

nal buffers are bypassed and powered down. When

this bit is set high, the buffers drive the input sampling

capacitors and minimize the dynamic input load.

DIFF:

(Default = 0) Differential/Pseudo-Differential Bit.

When DIFF = 0, the part is in pseudo-differential mode,

and AIN1–AIN5 are measured respective to AIN6, the

analog common. When DIFF = 1, the part is in differen-

tial mode with the analog inputs defined as AIN1/AIN2,

AIN3/AIN4, and AIN5/AIN6. The available input chan-

nels for each mode are tabulated in Table 5. Note that

DIFF also affects the scanning sequence when the part

is placed in SCAN mode (Table 4).

BOUT:

(Default = 0) Burn-out Current Bit. Setting BOUT

= 1 connects 100nA current sources to the selected

analog input channel. This mode is used to check that a

transducer has not burned out or opened circuit. The

burn-out current source must be turned off (BOUT = 0)

before measurement to ensure best linearity.

RESERVED:

(Default = 0) Reserved Bit. A 0 must be

written to this location.

X2CLK:

(Default = 0) Times-Two Clock Bit. Setting this

bit to 1 selects a divide-by-2 prescaler in the clock sig-

nal path. This allows use of a higher frequency crystal

or clock source and improves immunity to asymmetric

clock sources.

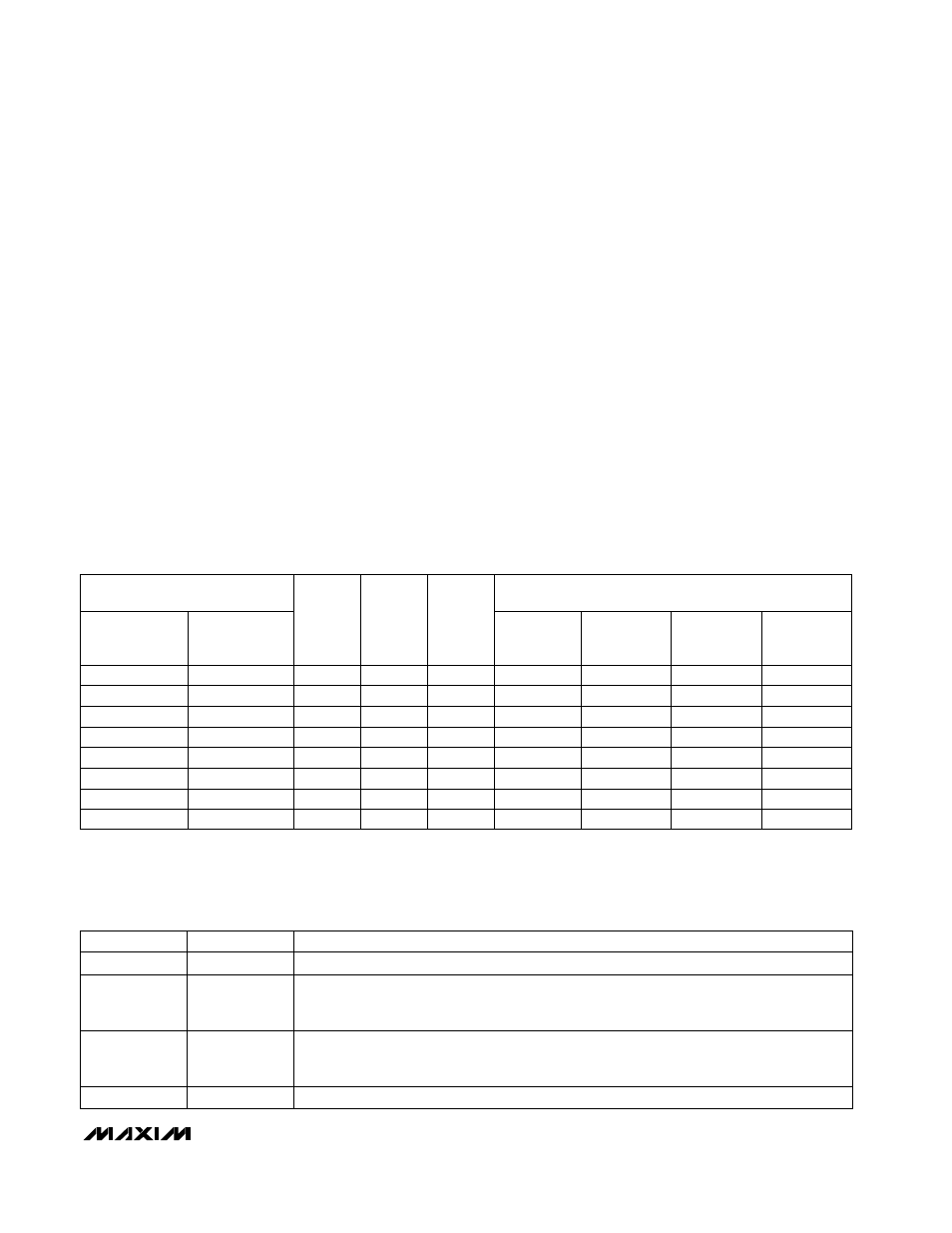

Table 2. Data Output Rate vs. CLK, Filter Select, and Modulator Frequency Bits

*

Data rates offering noise-free 16-bit resolution.

Note:

When FAST = 0, f

-3dB

= 0.262

·

Data Rate. When FAST = 1, f

-3dB

= 0.443

·

Data Rate.

Note:

Default condition is in bold print.

Table 3. Special Modes Controlled by M1, M0 (SCAN = 0)

1

0

1

0

1

0

1

0

MF0

1

1

0

0

1

1

0

0

MF1

1

1

1

1

0

0

0

0

CLK

2400

4800

400

480

4.9152

2.4576

1200

2400

200

240

4.9152

2.4576

600

1200

100

120

4.9152

2.4576

300

600

50

60

4.9152

2.4576

800

1600

160

200

2.048

1.024

400

800

80

100

2.048

1.024

200

400

40

50

2.048

1.024

FS1, FS0

(1, 0)

FS1, FS0

(1, 1)

FS1, FS0*

(0, 0)

100

AVAILABLE OUTPUT DATA RATES

(sps)

X2CLK = 0

200

FS1, FS0*

(0, 1)

20

25

X2CLK = 1

2.048

1.024

0

M0

1

Calibrate Offset:

In this mode the MAX1401 converts the voltage applied across CALOFF+

and CALOFF-. The PGA gain, DAC, and format settings of the selected channel (defined by

DIFF, A1, A0) are used.

0

0

1

Reserved:

Do not use.

1

Calibrate Gain:

In this mode the MAX1401 converts the voltage applied across CALGAIN+

and CALGAIN-. The PGA gain, DAC, and format settings of the selected channel (defined by

DIFF, A1, A0) are used.

Normal Mode:

The device operates normally.

1

0

M1

DESCRIPTION

CLKIN FREQUENCY,

f

CLKIN

(MHz)