Rainbow Electronics DS12887 User Manual

Page 10

DS12887

10 of 19

changed. Therefore, the user should avoid interrupt service routines that would cause the time needed to

read valid time/calendar data to exceed 244

ms.

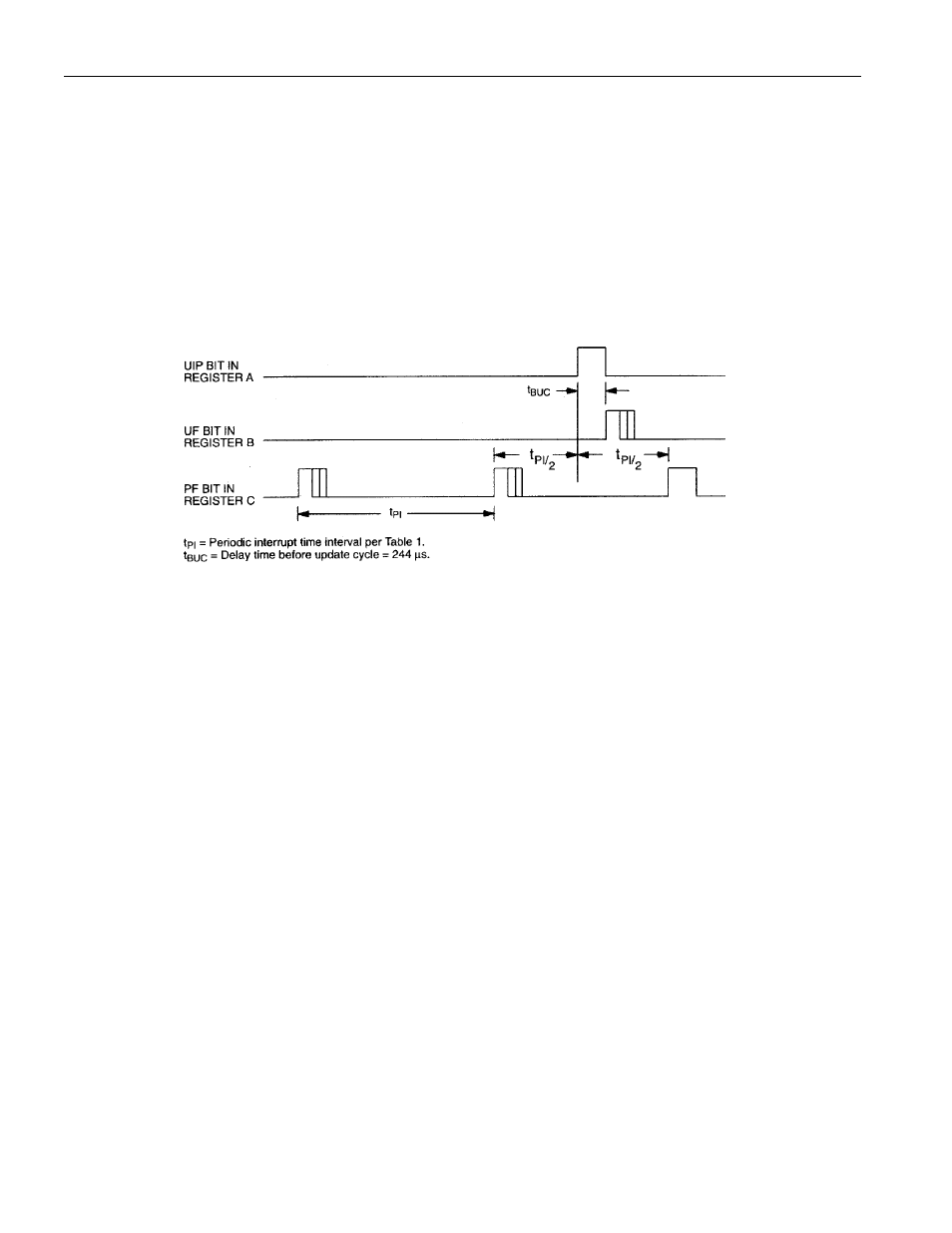

The third method uses a periodic interrupt to determine if an update cycle is in progress. The UIP bit in

Register A is set high between the setting of the PF bit in Register C (Figure 3). Periodic interrupts that

occur at a rate of greater than t

BUC

allow valid time and date information to be reached at each occurrence

of the periodic interrupt. The reads should be complete within one (t

PI/2

+ t

BUC

) to ensure that data is not

read during the update cycle.

Figure 3. UPDATE-ENDED AND PERIODIC INTERRUPT RELATIONSHIP

See also other documents in the category Rainbow Electronics Computer hardware:

- MAX6869 (17 pages)

- TNY-A9260-C01 (5 pages)

- MAX34441 (53 pages)

- MAX4912 (13 pages)

- QIL-A9260-C11 (1 page)

- QIL-A9260-C11 (34 pages)

- QIL-A9260-C11 (20 pages)

- USB-A9263-C02 (1 page)

- DAB-GPS-C01 (15 pages)

- DAB-GPS-C01 (28 pages)

- DAB-CAM-C01 (27 pages)

- DAB-WLS-C01 (WiFi) (20 pages)

- USB-A9G20-C01 (1 page)

- MAX34440 (43 pages)

- SBC35-A9260-C12 (28 pages)

- SBC35-A9260-C12 (1 page)

- MAX16024 (17 pages)

- USB-A9G20-C11 (5 pages)

- DAB-IMU-C01 (20 pages)

- MAX16021 (21 pages)

- DAB-WLS-C11 (BlueTooth) (2 pages)

- SBC35-A9G20-C11 (24 pages)

- MAX16054 (9 pages)

- MAX14525 (7 pages)

- MAX16066 (61 pages)

- USB-A9260-C12 (1 page)

- DS1803 (11 pages)

- DS12887A (2 pages)

- DS1339 (18 pages)

- DS1858 (22 pages)

- DS1267 (12 pages)

- DS12С887A (2 pages)

- DS1804 (7 pages)

- DS1091L (6 pages)

- DS1669S (10 pages)

- DS1867 (14 pages)

- DS1087L (12 pages)

- DS4026 (13 pages)

- DS1286 (13 pages)

- DS1801 (10 pages)

- DS1254 (17 pages)

- DS17887 (38 pages)

- DS1691 (4 pages)

- DS1615 (24 pages)

- DS1868 (14 pages)