Ac timing characteristics – 3.3v operation, Tion, At6000(lv) series – Rainbow Electronics AT6010LV User Manual

Page 20

AT6000(LV) Series

20

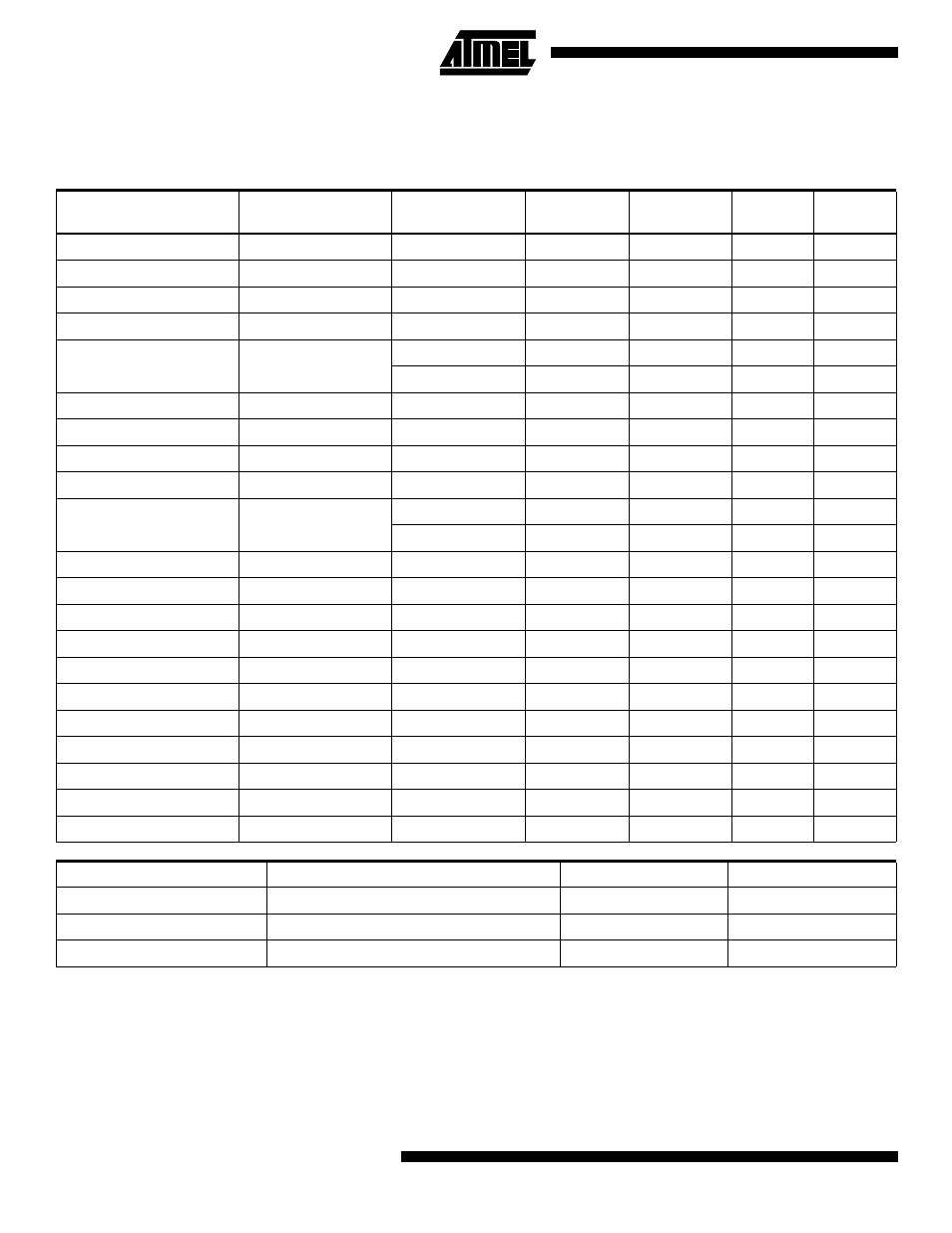

AC Timing Characteristics – 3.3V Operation

Notes:

1. TTL buffer delays are measured from a V

IH

of 1.5V at the pad to the internal V

IH

at A. The input buffer load is constant.

2. CMOS buffer delays are measured from a V

IH

of 1/2 V

CC

at the apd to the internal V

IH

at A. The input buffer load is constant.

3. Buffer delay is to a pad voltage of 1.5V with one output switching.

4. Max specifications are the average of mas t

PDLH

and t

PDHL

.

5. Parameter based on characterization and simulation; not tested in production

6. Exact power calculation is available in an Atmel application note.

7. Load Definition: 1 = Load of one A or B input; 2 = Load of one L input; 3 = Constant Load; 4 = Load of 28 Clock Columns; 5

= Load of 28 Reset Columns; 6 = Tester Load of 50 pF.

Delays are based on fixed load. Loads for each type of device are described in the notes. Delays are in nanoseconds.

Worst case: V

CC

= 3.0V to 3.6V. Temperature = 0

°

C to 70

°

C.

Cell Function

Parameter

From

To

Load

Definition

-4

Units

Wire

t

PD

(max)

A, B, L

A, B

1

1.8

ns

NAND

t

PD

(max)

A, B, L

B

1

3.2

ns

XOR

t

PD

(max)

A, B, L

A

1

4.0

ns

AND

t

PD

(max)

A, B, L

B

1

3.2

ns

MUX

t

PD

(max)

A, B

A

1

4.0

ns

L

A

1

4.9

ns

D-Flip-flop

t

setup

(min)

A, B, L

CLK

-

3.0

ns

D-Flip-flop

t

hold

(min)

CLK

A, B, L

-

0

ns

D-Flip-flop

t

PD

(max)

CLK

A

1

3.0

ns

Bus Driver

t

PD

(max)

A

L

2

4.0

ns

Repeater

t

PD

(max)

L, E

E

3

2.3

ns

L, E

L

2

3.0

ns

Column Clock

t

PD

(max)

GCLK, A, ES

CLK

3

3.0

ns

Column Reset

t

PD

(max)

GRES, A, EN

RES

3

3.0

ns

Clock Buffer

t

PD

(max)

CLOCK PIN

GCLK

4

2.9

ns

Reset Buffer

t

PD

(max)

RESET PIN

GRES

5

2.8

ns

TTL Input

t

PD

(max)

I/O

A

3

1.5

ns

CMOS Input

t

PD

(max)

I/O

A

3

2.3

ns

Fast Output

t

PD

(max)

A

I/O PIN

6

6.0

ns

Slow Output

t

PD

(max)

A

I/O PIN

6

12.0

ns

Output Disable

t

PXZ

(max)

L

I/O PIN

6

5.5

ns

Fast Enable

t

PXZ

(max)

L

I/O PIN

6

6.5

ns

Slow Enable

t

PXZ

(max)

L

I/O PIN

6

12.5

ns

Device

Cell Types

Outputs

I

CC

(max)

Cell

Wire, XWire, Half-adder, Flip-flop

A, B

2.3 µA/MHz

Bus

Wire, XWire, Half-adder, Flip-flop, Repeater

L

1.3 µA/MHz

Column Clock

Column Clock Driver

CLK

20 µA/MHz