Rainbow Electronics MAX8709 User Manual

Page 16

MAX8709

High-Efficiency CCFL Backlight

Controller with SMBus Interface

16

______________________________________________________________________________________

SMBus Interface (SDA, SCL)

The MAX8709 supports an Intel SMBus-compatible 2-

wire digital interface. SDA is the bidirectional data line

and SCL is the clock line of the 2-wire interface corre-

sponding respectively to SMBDATA and SMBCLK lines

of the SMBus. SDA and SCL are Schmidt-triggered

inputs that can accommodate slow edges; however,

the rising and falling edges should still be faster than

1µs and 300ns, respectively. The MAX8709 uses the

write-byte, read-byte, and receive-byte protocols

(Figure 7). The SMBus protocols are documented in

System Management Bus Specification V1.1 and avail-

able at http://www.SMBus.org/.

The MAX8709 is a slave-only device and responds to

the 7-bit address 0b01011000 (i.e., with the R/

W bit

clear indicating a write, this corresponds to 0x58). The

MAX8709 has three functional registers: a 5-bit bright-

ness register (BRIGHT4–BRIGHT0), a 3-bit shutdown-

mode register (SHMD2–SHMDE0), and a 2-bit status

register (STATUS1–STATUS0). In addition, the device

has three identification (ID) registers: an 8-bit chip ID

register, an 8-bit chip revision register, and an 8-bit

manufacturer ID register.

Communication starts with the master signaling the

beginning of a transmission with a START condition,

which is a high-to-low transition on SDA while SCL is

high. When the master has finished communicating with

the slave, the master issues a STOP condition, which is

a low-to-high transition on SDA while SCL is high. The

bus is then free for another transmission. Figures 8 and

9 show the timing diagrams for signals on the 2-wire

interface. The address byte, command byte, and data

byte are transmitted between the START and STOP con-

ditions. The SDA state is allowed to change only while

SCL is low, except for the START and STOP conditions.

Data is transmitted in 8-bit words and is sampled on the

rising edge of SCL. Nine clock cycles are required to

transfer each byte in or out of the MAX8709 since either

the master or the slave acknowledges the receipt of the

correct byte during the ninth clock. If the MAX8709

receives its correct slave address followed by R/W = 0,

it expects to receive 1 or 2 bytes of information

(depending on the protocol). If the device detects a

START or STOP condition prior to clocking in the bytes

of data, it considers this an error condition and disre-

gards all of the data.

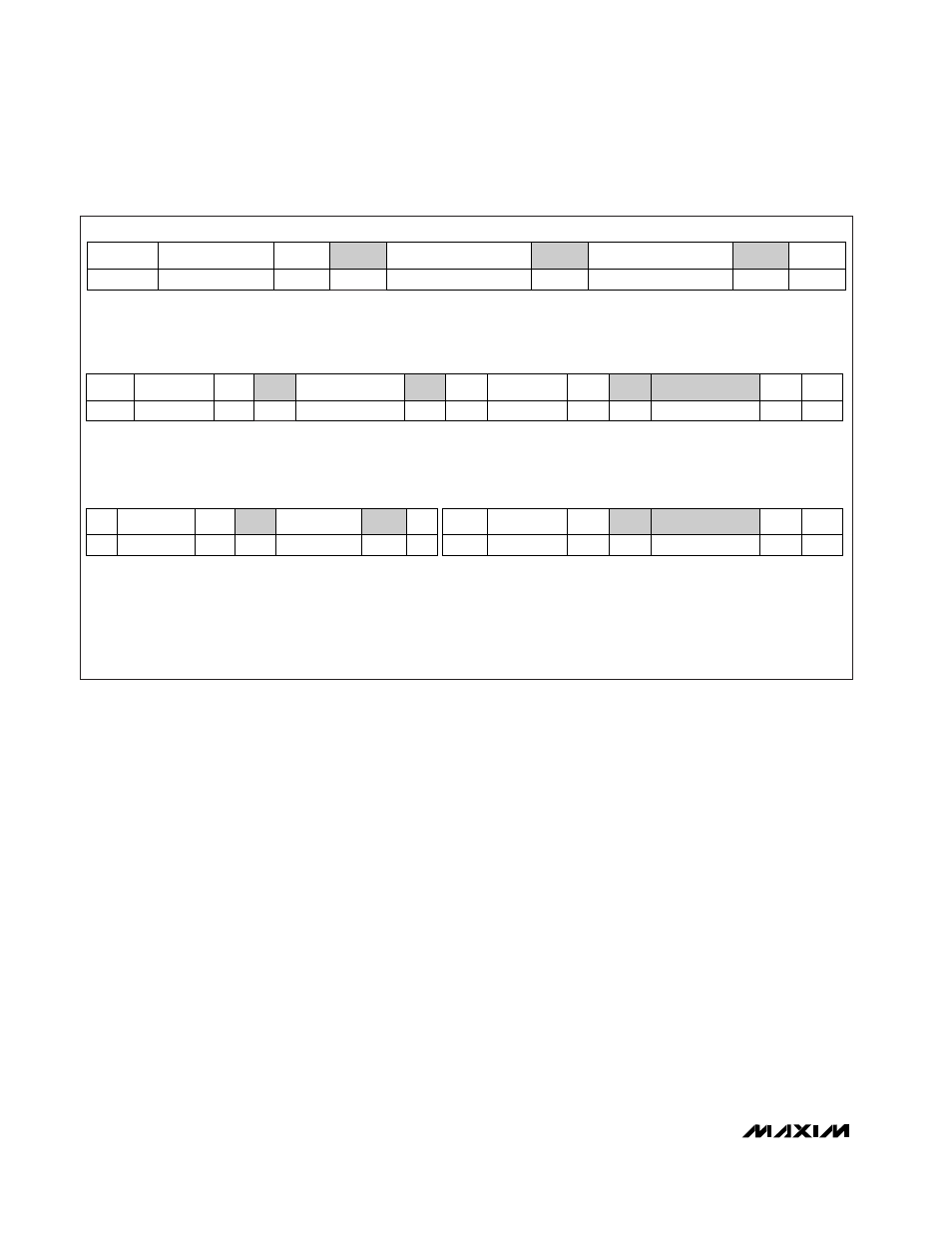

1b

ACK

1b

7 bits

ADDRESS

ACK

1b

WR

8 bits

DATA

1b

ACK

P

8 bits

S

COMMAND

Write-Byte Format

Receive-Byte Format

Slave Address

Command Byte: selects

which register you are

writing to

Data Byte: data goes into the register

set by the command byte

1b

ACK

1b

7 bits

ADDRESS

ACK

1b

WR

S

1b

ACK

8 bits

DATA

7 bits

ADDRESS

1b

RD

1b

8 bits

///

P

S

COMMAND

Slave Address

Slave Address

Command Byte: sends command

with no data; usually used for one-

shot command

Command Byte: selects

which register you are

reading from

Slave Address: repeated

due to change in data-

flow direction

Data Byte: reads from

the register set by the

command byte

1b

ACK

7 bits

ADDRESS

1b

RD

8 bits

DATA

1b

///

P

S

Data Byte: reads data from

the register commanded

by the last read-byte or

write-byte transmission;

also used for SMBus Alert

Response return address

S = Start condition

Shaded = Slave transmission

WR = Write = 0

P = Stop condition

Ack= Acknowledged = 0

RD = Read =1

/// = Not acknowledged = 1

1b

ACK

7 bits

ADDRESS

1b

WR

8 bits

COMMAND

1b

ACK

P

S

Send-Byte Format

Read-Byte Format

Figure 7. SMBus Protocols