Max5945, Quad network power controller for power-over-lan, Table 12a. detection result decoding chart – Rainbow Electronics MAX5945 User Manual

Page 26: Table 12b. classification result decoding chart

MAX5945

function. OSC_FAIL generates an interrupt only if at

least one of the ACD_EN (R13h[7:4]) bits is set high.

A thermal-shutdown circuit monitors the temperature of

the die and resets the MAX5945 if the temperature

exceeds +150°C. TSD is set to 1 after the MAX5945

returns to normal operation. TSD is also set to 1 after

every UVLO reset.

When V

DD

and/or |V

EE

| is below its undervoltage lock-

out (UVLO) threshold, the MAX5945 is in reset mode

and securely holds all ports off. When V

DD

and |V

EE

|

rise to above their respective UVLO thresholds, the

device comes out of reset as soon as the last supply

crosses the UVLO threshold. The last supply corre-

sponding UV and UVLO bits in the supply event regis-

ter will be set to 1.

A 1 in any supply event register’s bits forces R00h[7] to

1. As with any other events register, the supply event

register has two addresses. When read through the

R0Ah address, the content of the register is left

unchanged. When read through the CoR R0Bh

address, the register content will be cleared. A reset

sets R0Ah/R0Bh to 00100001 if V

DD

comes up after

V

EE

or to 00010100 if V

EE

comes up after V

DD

.

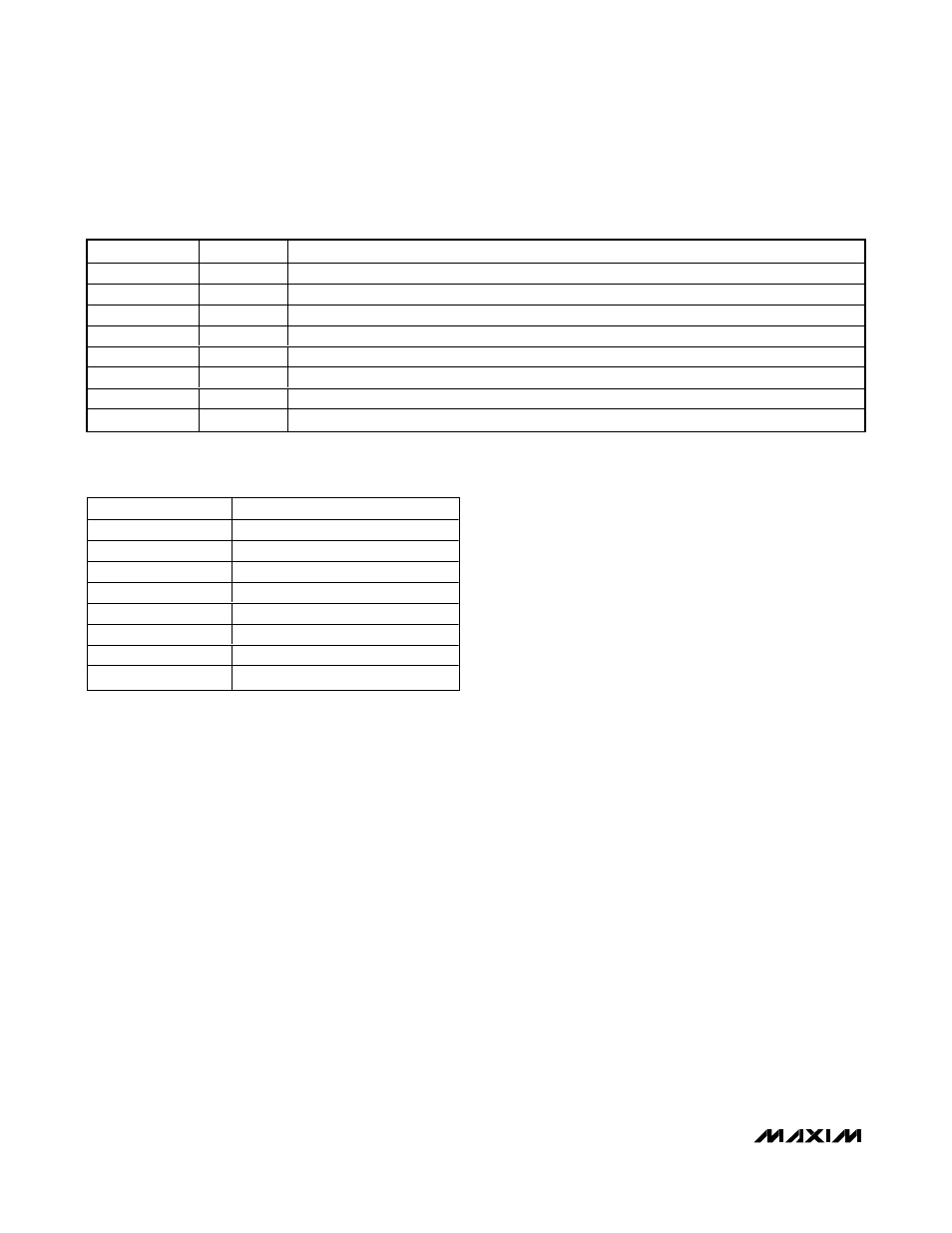

The port status register (Table 12) records the results of

the detection and classification at the end of each phase

in three encoding bits each. R0Ch contains detection and

classification status of port 1. R0Dh corresponds to port

2, R0Eh corresponds to port 3 and R0Fh corresponds to

port 4. Tables 12a and 12b show the detection/classifica-

tion result decoding charts, respectively.

As a protection, when POFF_CL (R17h[3], Table 20) is

set to 1, the MAX5945 prohibits turning on power to the

port that returns a status 111 after classification. A reset

sets 0Ch, 0Dh, 0Eh, and 0Fh = 00h.

PGOOD_ is set to 1 (Table 13) at the end of the power-up

startup period if the power-good condition is met (0 <

(V

OUT

- V

EE)

< PG

TH

). The power-good condition must

remain valid for more than t

PGOOD

to assert PGOOD_.

PGOOD_ is reset to 0 whenever the output falls out of the

power-good condition. A fault condition immediately

forces PGOOD_ low.

PWR_EN_ is set to 1 when the port power is turned on.

PWR_EN_ resets to 0 as soon as the port turns off. Any

transition of PGOOD_ and PWR_EN_ bits set the corre-

sponding bit in the power event registers R02h/R03h

(Table 7). A reset sets R10h = 00h.

A3, A2, A1, A0 (Table 14) represent the four LSBs of the

MAX5945 address (Table 3). During a reset, the device

latches into R11h. These four bits address from the cor-

responding inputs as well as the state of the MIDSPAN

and AUTO inputs. Changes to those inputs during nor-

mal operation are ignored.

The MAX5945 uses two bits for each port to set the mode

of operation (Table 15). Set the modes according to

Table 15a.

A reset sets R12h = AAAAAAAA where A represents

the latched-in state of the AUTO input prior to the reset.

Use software to change the mode of operation.

Quad Network Power Controller

for Power-Over-LAN

26

______________________________________________________________________________________

DET_ST_[2:0]

DETECTED

DESCRIPTION

000

None

Detection status unknown

001

DCP

Positive DC supply connected at the port (AGND - V

OUT_

< 1.65V)

010

HIGH CAP

High capacitance at the port (>5µF)

011

RLOW

Low resistance at the port. R

PD

< 17k

Ω.

100

DET_OK

Detection pass. 17k

Ω > R

PD

> 28k

Ω.

101

RHIGH

High resistance at the port. R

PD

> 28k

Ω.

110

OPEN0

Open port (I < 12.5µA)

111

DCN

Negative DC supply connected to the port (V

OUT

- V

EE

< 2V)

Table 12a. Detection Result Decoding Chart

CLASS_[2:0]

CLASS RESULT

000

Unknown

001

1

010

2

011

3

100

4

101

Undefined (treated as CLASS 0)

110

0

111

Current limit (>I

CILIM

)

Table 12b. Classification Result

Decoding Chart