Pin description (continued) – Rainbow Electronics MAX17036 User Manual

Page 13

MAX17030/MAX17036

1/2/3-Phase Quick-PWM

IMVP-6.5 VID Controllers

______________________________________________________________________________________

13

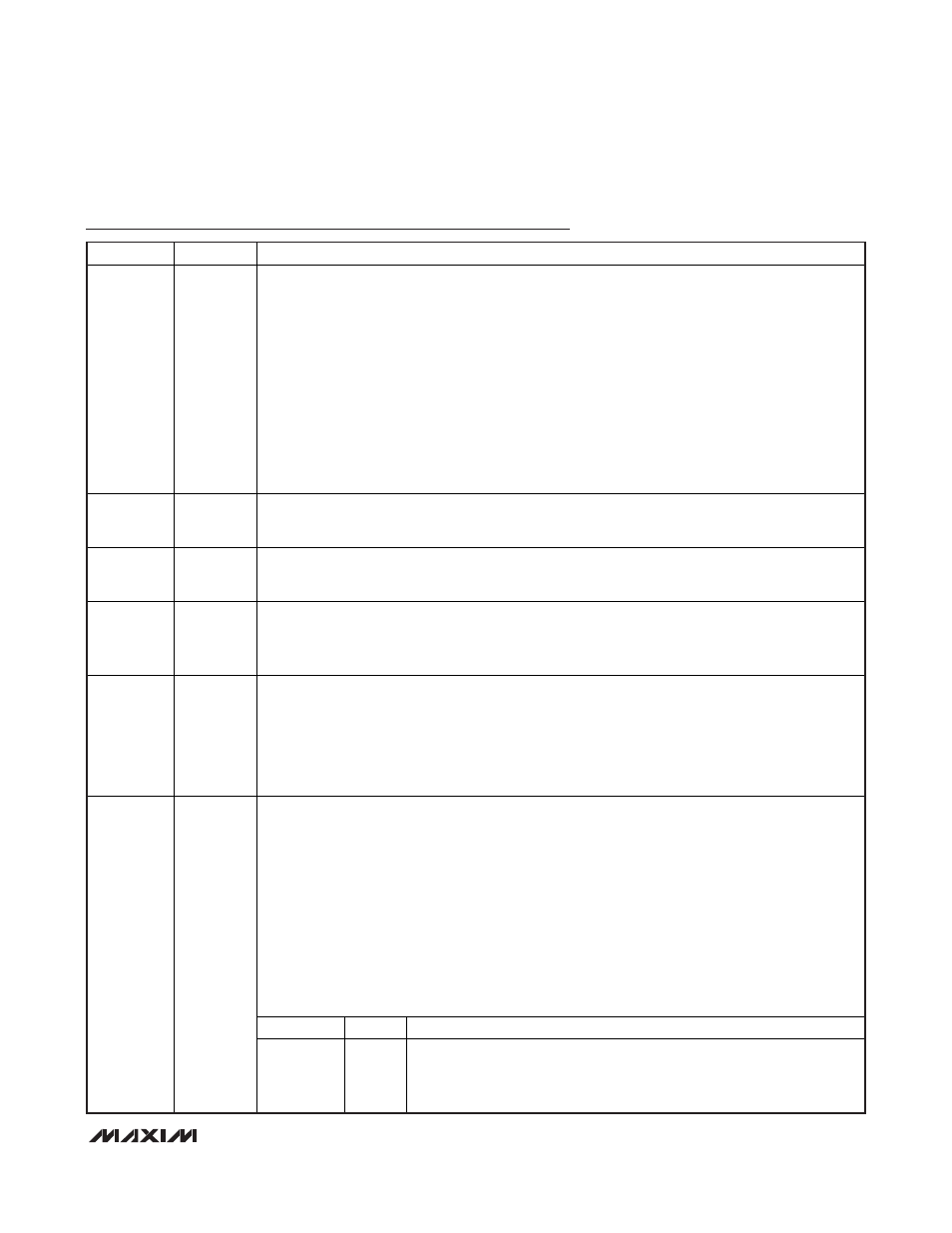

Pin Description (continued)

PIN

NAME

FUNCTION

9 FBAC

Output of the Voltage-Positioning Transconductance Amplifier. Connect a resistor R

FBAC

between

FBAC and the positive side of the feedback remote sense to set the transient (AC) droop based on

the stability, load-transient response, and voltage-positioning gain requirements:

R

FBAC

= R

DROOP,AC

/[R

SENSE

x G

m(FBAC)

]

where R

DROOP,AC

is the transient (AC) voltage-positioning slope that provides an acceptable

tradeoff between stability and load-transient response, G

m(FBAC)

= 400µS typ, and R

SENSE

is the

effective current-sense resistance that is used to provide the (CSP_, CSN_) current-sense voltages.

A minimum R

DROOP,AC

value is required for stability, but if there are no ceramic output capacitors

used, then the minimum requirement applies to R

ESR

+ R

DROOP,AC

, where R

ESR

is the effective

ESR of the output capacitors.

If lossless sensing (inductor DCR sensing) is used, use a thermistor-resistor network to minimize

the temperature dependence of the voltage-positioning slope.

FBAC is high impedance in shutdown.

10 GNDS

Feedback Remote-Sense Input, Negative Side. Normally connected to GND directly at the load.

GNDS internally connects to a transconductance amplifier that fine tunes the output voltage

compensating for voltage drops from the regulator ground to the load ground.

11 CSN2

Negative Input of the Output Current Sense of Phase 2. This pin should be connected to the

negative side of the output current-sensing resistor or the filtering capacitor if the DC resistance of

the output inductor is utilized for current sensing.

12 CSP2

Positive Input of the Output Current Sense of Phase 2. This pin should be connected to the positive

side of the output current-sensing resistor or the filtering capacitor if the DC resistance of the output

inductor is utilized for current sensing.

To disable phase 2, connect CSP2 to V

CC

and CSN2 to GND.

13

SHDN

Shutdown Control Input. Connect to V

CC

for normal operation. Connect to ground to put the IC into

the 1µA (max at T

A

= +25

°C) shutdown state. During startup, the output voltage is ramped up at 1/4

the slew rate set by the TIME resistor to the boot voltage or to the target voltage.

During the transition from normal operation to shutdown, the output voltage is ramped down at 1/6

the slew rate set by the TIME resistor. Forcing

SHDN to 11V~13V to enter no-fault test mode clears

the fault latches, disables transient phase overlap, and turns off the internal BST_-to-V

DD

switches.

However, internal diodes still exist between BST_ and V

DD

in this state.

Deeper Sleep VR Control Input. This low-voltage logic input indicates power usage and sets the

operating mode together with

PSI as shown in the truth table below. When DPRSLPVR is forced high, the

controller is immediately set to 1-phase automatic pulse-skipping mode. The controller returns to forced-

PWM mode when DPRSLPVR is forced low and the output is in regulation. The PWRGD upper threshold

is blanked during any downward output-voltage transition that happens when the controller is in skip

mode, and stays blanked until the slew-rate-controlled internal-transition-related PWRGD blanking period

is complete and the output reaches regulation. During this blanking period, the overvoltage fault

threshold is changed from a tracking [VID + 300mV] threshold to a fixed 1.5V threshold.

The controller is in N-phase skip mode during startup including boot mode, but is in N-phase

forced-PWM mode during the transition from boot mode to VID mode, during soft-shutdown,

irrespective of the DPRSLPVR and

PSI logic levels. However, if phases 2 and 3 are disabled by

connecting CSP2, CSP3 to V

CC

, then only phase 1 is active in the above modes.

DPRSLPVR

PSI

MODE

14 DPRSLPVR

1

0

0

X

0

1

Very low current (1-phase skip)

Intermediate power potential (N-1-phase PWM)

Max power potential (full-phase PWM: N-phase or 1 phase as set by user

at CSP2, CSP3)