Step immunity and no r, Sense – Rainbow Electronics MAX5937 User Manual

Page 18

MAX5936/MAX5937

-48V Hot-Swap Controllers with V

IN

Step Immunity and No R

SENSE

18

______________________________________________________________________________________

Power-Up to Fault Management:

1) Same as step 1 above. [GATE turn-on]

2) Same as step 2 above. [V

OUT

ramp]

3) GATE ramps to 90% of full enhancement while

V

OUT

remains above 72% V

CB

, at which point the

GATE is rapidly pulled to V

EE

and fault manage-

ment is initiated. [Fault management]

GATE Cycle During V

IN

Step

A step GATE cycle occurs only after a successful

power-up GATE cycle to full enhancement occurs and

as a result of a positive V

IN

step (all voltages are

relative to V

EE

).

Step to Full Enhancement:

1) A V

IN

step occurs resulting in STEP_MON rising

above STEP

TH

before V

OUT

rises above V

SC

. [Step

detection]

2) After a step is detected, V

OUT

rises above V

SC

in

response to the step. When V

OUT

rises above V

SC

,

GATE is immediately pulled to V

EE

, rapidly turning off

the power MOSFET. GATE is held at V

EE

for 350µs to

dampen any ringing. Once GATE is pulled to V

EE

,

the gate cycle has begun and STEP_MON can safely

drop below STEP

TH

and successfully complete a

step GATE cycle to full enhancement without initiat-

ing fault management. [GATE pulldown]

3) Following the 350µs of GATE pulldown, GATE is

allowed to float for 650µs. At this point, the GATE

begins to ramp with 52µA charging the gate of the

power MOSFET. [GATE turn-on]

4) When GATE reaches the gate threshold voltage of

the power MOSFET, V

OUT

begins to ramp down

toward the new lower V

EE

. In the interval where

GATE is below the MOSFET threshold, the MOSFET

is off and V

OUT

will droop depending on the RC

time constant of the load. [V

OUT

ramp]

5) When V

OUT

ramps below 72% V

CB

, the GATE pulls

rapidly to full enhancement and the step GATE

cycle is complete. If STEP_MON remains above

STEP

TH

when GATE has ramped to 90% of full

enhancement and V

OUT

remains above 72% of

V

CB

, GATE remains at 90% and will not be pulled to

full enhancement. In this condition, if V

OUT

drops

below 72% of V

CB

before STEP_MON drops below

STEP

TH

, GATE is rapidly pulled to full enhancement

and the step GATE cycle is complete. PGOOD

remains asserted throughout the step GATE cycle.

[Full enhancement]

Step to Fault Management:

1) Same as step 1 above. [Step detection]

2) Same as step 2 above. [GATE pulldown]

3) Same as step 3 above. [GATE turn-on]

4) Same as step 4 above. [VOUT ramp]

5) If STEP_MON is below STEP

TH

when GATE ramps

to 90% of full enhancement and V

OUT

remains

above 72% V

CB,

GATE is rapidly pulled to V

EE

.

Fault management is initiated and PGOOD is de-

asserted. If STEP_MON is above STEP

TH

when

GATE ramps to 90% of full enhancement and V

OUT

remains above 72% of V

CB

, GATE remains at 90%.

It will not be pulled to full enhancement nor will it be

pulled to V

EE

. In this condition, if V

OUT

drops below

72% of V

CB

before STEP_MON drops below

STEP

TH

, GATE is rapidly pulled to full enhancement

and a fault is avoided. Conversely, if STEP_MON

drops below STEP

TH

first, the GATE is rapidly

pulled to V

EE

, fault management is initiated, and

PGOOD is deasserted. [Fault management]

It should be emphasized that while STEP_MON remains

above STEP

TH

the current fault management is

blocked. During this time it is possible for there to be

multiple events involving V

OUT

rising above V

SC

then

those falling below 75% V

CB

. In each of these events,

when V

OUT

rises above V

SC

, a full GATE cycle is initiat-

ed where GATE is first pulled low then allowed to ramp

up. Then finally, when V

OUT

conditions are met, it will

be fully enhanced.

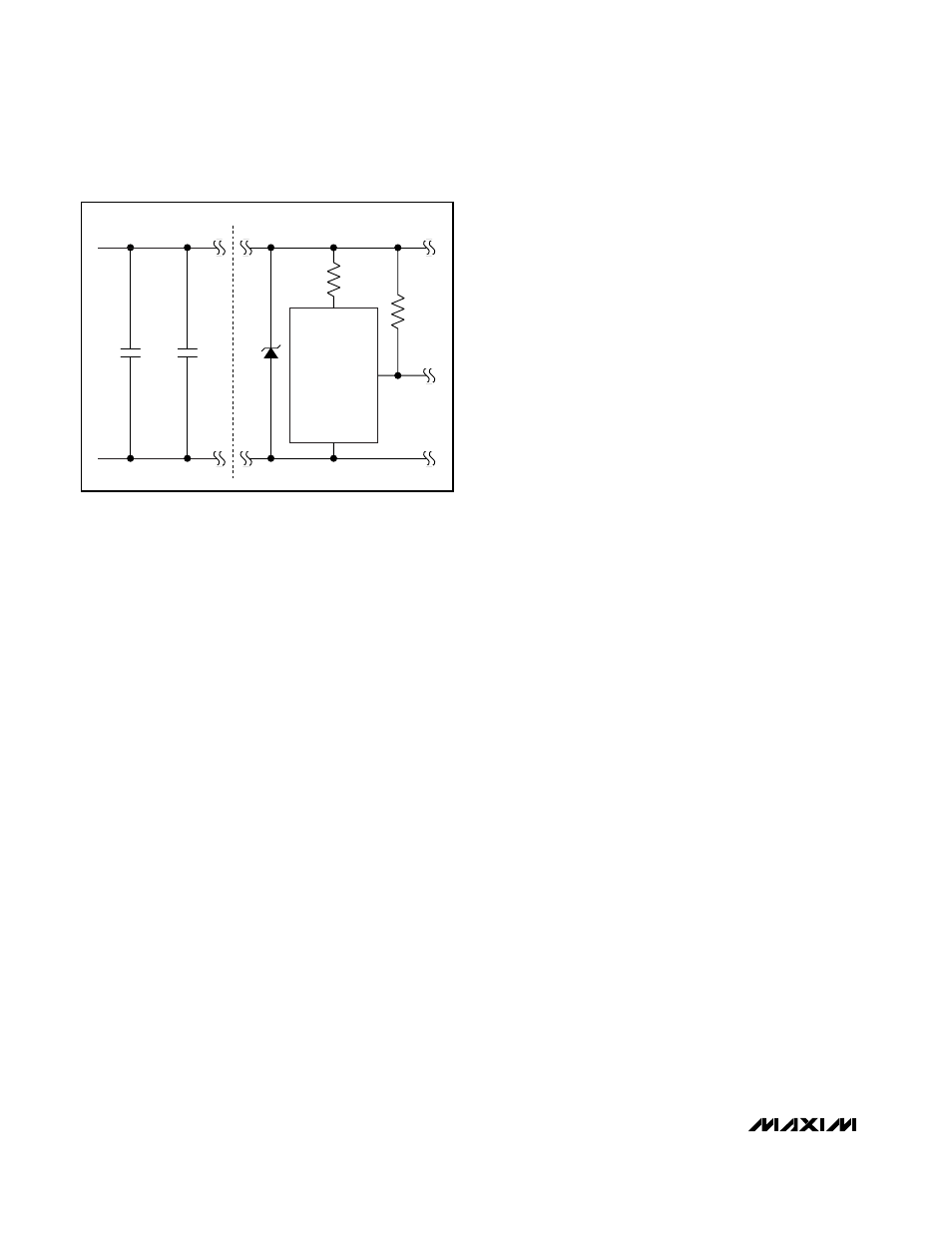

Figure 17. Protecting the MAX5936/MAX5937 Input from High-

Voltage Transients

0.1µF

1µF

68V

TVS

1kΩ

100kΩ

V

EE

PGOOD

GND

BACKPLANE

48V ±10%

PLUG-IN CARD