Recommended dc operating conditions (continued) – Rainbow Electronics MAXQ2010 User Manual

Page 8

MAXQ2010

16-Bit Mixed-Signal Microcontroller with LCD

8

_______________________________________________________________________________________

Note 12: Programming time does not include overhead associated with the utility ROM interface.

Note 13: V

REF

= AV

DD

.

Note 14: The operational input voltage range for each individual input of a differentially configured pair is from GND to AVDD. The

operational input voltage difference is from -V

REF

/2 to +V

REF

/2.

Note 15: The typical value is applied when a conversion is requested with ADPMO = 0. Under these conditions, the minimum delay

is met. If ADPMO = 1, the user is responsible for ensuring the 4µs delay time is met.

Note 16: Switching ADC reference from either internal or external reference to AVDD. Sample accuracy is not guaranteed prior to

ADC reference settlement.

Note 17: Total on-board decoupling capacitance on the AVDD pin < 100nF. The output impedance of the regulator driving the

AVDD pin < 10

Ω.

Note 18: This parameter is guaranteed by design and is not production tested.

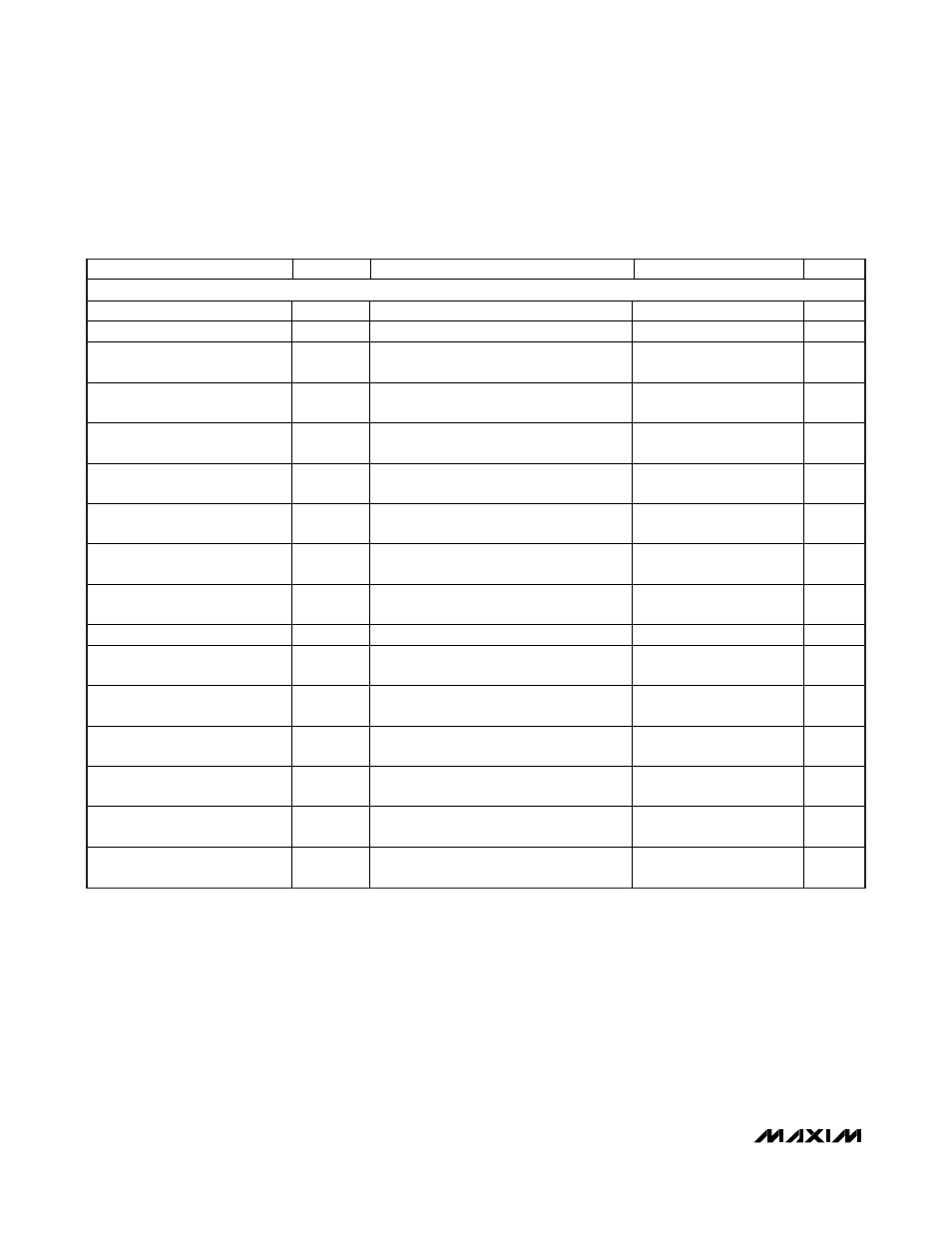

RECOMMENDED DC OPERATING CONDITIONS (continued)

(V

DVDD

= V

AVDD

= 2.7V to 3.6V, T

A

= -40°C to +85°C.) (Note 1)

PARAMETER SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

SPI (See Figures 1 and 2)

SPI Master Operating Frequency

1/t

MCK

f

CK

/2 MHz

SPI Slave Operating Frequency

1/t

SCK

f

CK

/8 MHz

SCLK Output Pulse-Width

High/Low

t

MCH

, t

MCL

(t

MCK

/2)

- 25

ns

SCLK Input Pulse-Width

High/Low

t

SCH

, t

SCL

t

SCK

/2

ns

MOSI Output Hold Time After

SCLK Sample Edge

t

MOH

C

L

= 50pF

(t

MCK

/2)

- 25

ns

MOSI Output Valid to Sample

Edge

t

MOV

(t

MCK

/2)

- 25

ns

MISO Input Valid to SCLK

Sample Edge Rise/Fall Setup

t

MIS

25

ns

MISO Input to SCLK Sample

Edge Rise/Fall Hold

t

MIH

0

ns

SCLK Inactive to MOSI Inactive

t

MLH

(t

MCK

/2)

- 25

ns

SSEL Active to First Shift Edge

t

SSE

4t

CK

ns

MOSI Input to SCLK Sample

Edge Rise/Fall Setup

t

SIS

20

ns

MOSI Input from SCLK Sample

Edge Transition Hold

t

SIH

t

CK

+

25

ns

MISO Output Valid After SCLK

Shift Edge Transition

t

SOV

3t

CK

+

25

ns

SSEL Inactive

t

SSH

t

CK

+

25

ns

SCLK Inactive to

SSEL Rising

t

SD

t

CK

+

25

ns

MISO Output Disabled After

SSEL Edge Rise

t

SLH

2t

CK

+

50

ns