Figure 13, Th7887a – Rainbow Electronics TH7887A User Manual

Page 13

13

TH7887A

2146A–IMAGE–05/02

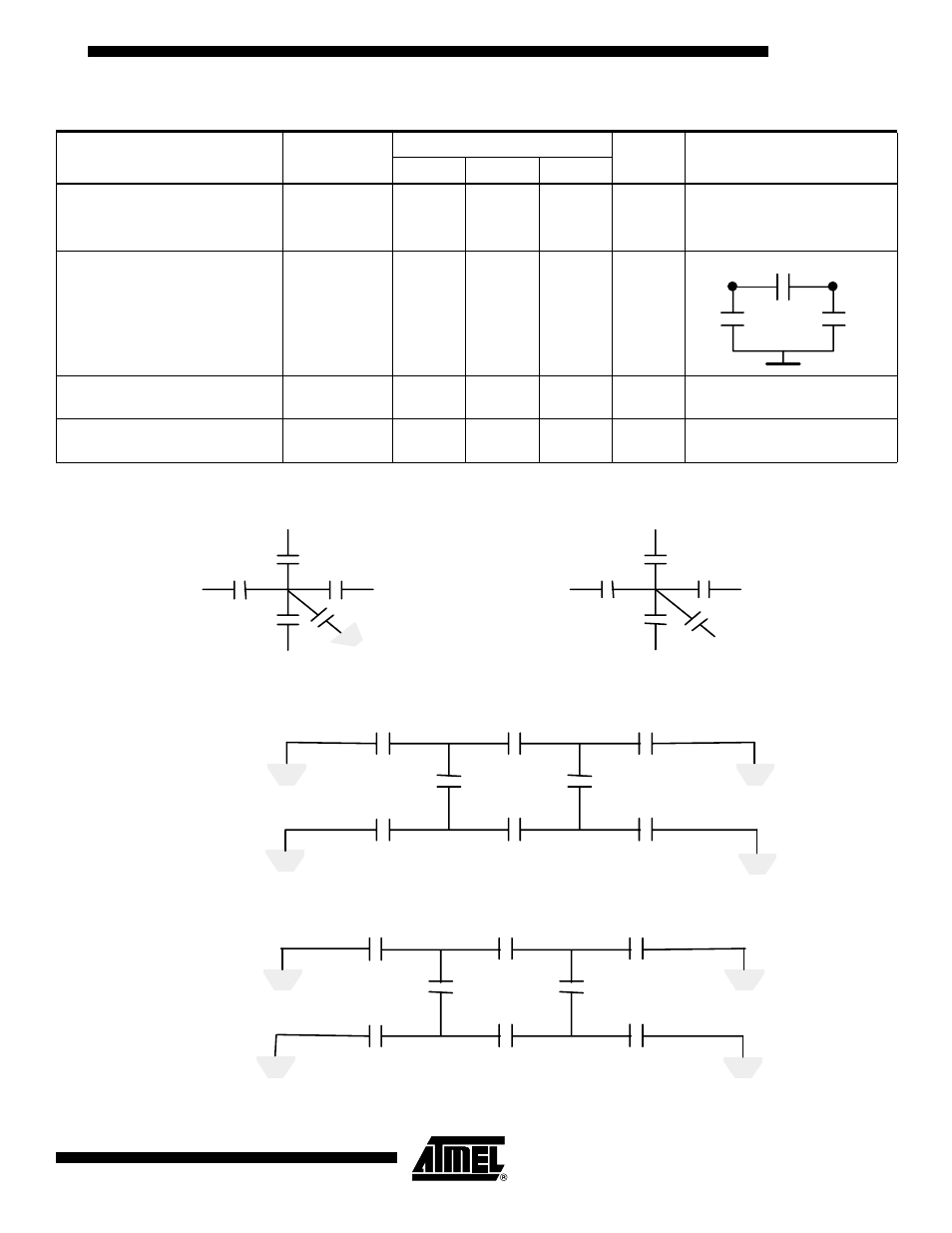

Figure 13. Capacitance Network for Drive Clocks

Reset gate

High level

Low level

ΦR

10

0

11

0.5

12

0.8

V

V

Typical input capacitance

10 pF

Readout register clocks

High level

Low level

ΦL1, 2

8.5

0

9

0.5

9.5

0.8

V

V

Maximum readout register

frequency

ΦF

H

–

20

23

MHz

See Figure 9

Image zone to memory zone

transfer frequency

ΦF

V

–

1.25

1.7

MHz

See Figure 14

Table 2. Drive Clock Characteristics (Continued)

Parameter

Symbol

Value

Unit

Remarks

Min

Typ

Max

60 pF

75 pF

50 pF

Φ

L1

Φ

L2

2.5 nF

1.4 nF

3.2 nF

4.9 nF

2.2 nF

3.3 nF

3.4 nF

2.5 nF

Φ

P1

Φ

P2

Φ

P3

Φ

P4

Φ

P1

Φ

P2

2.2 nF

4.4 nF

4.4 nF

4.4 nF

3.4 nF

Φ

P4

Φ

P3

3.9 nF

4.4 nF

3.2 nF

Φ

M1

Φ

M2

3.2 nF

4.4 nF

4.4 nF

4.4 nF

3.9 nF

Φ

M4

Φ

M3

Φ

A

0.5 nF

0.7 nF

1.3 nF

0.7 nF

0.5 nF

Φ

P1

Φ

P2

Φ

P3

Φ

P4

Φ

A

VA