5 interrupt status/clear register (intstatclr), Section 3.4, Section 3.5 – Texas Instruments VLYNQ Port User Manual

Page 31

www.ti.com

3.4

Interrupt Priority Vector Status/Clear Register (INTPRI)

3.5

Interrupt Status/Clear Register (INTSTATCLR)

VLYNQ Port Registers

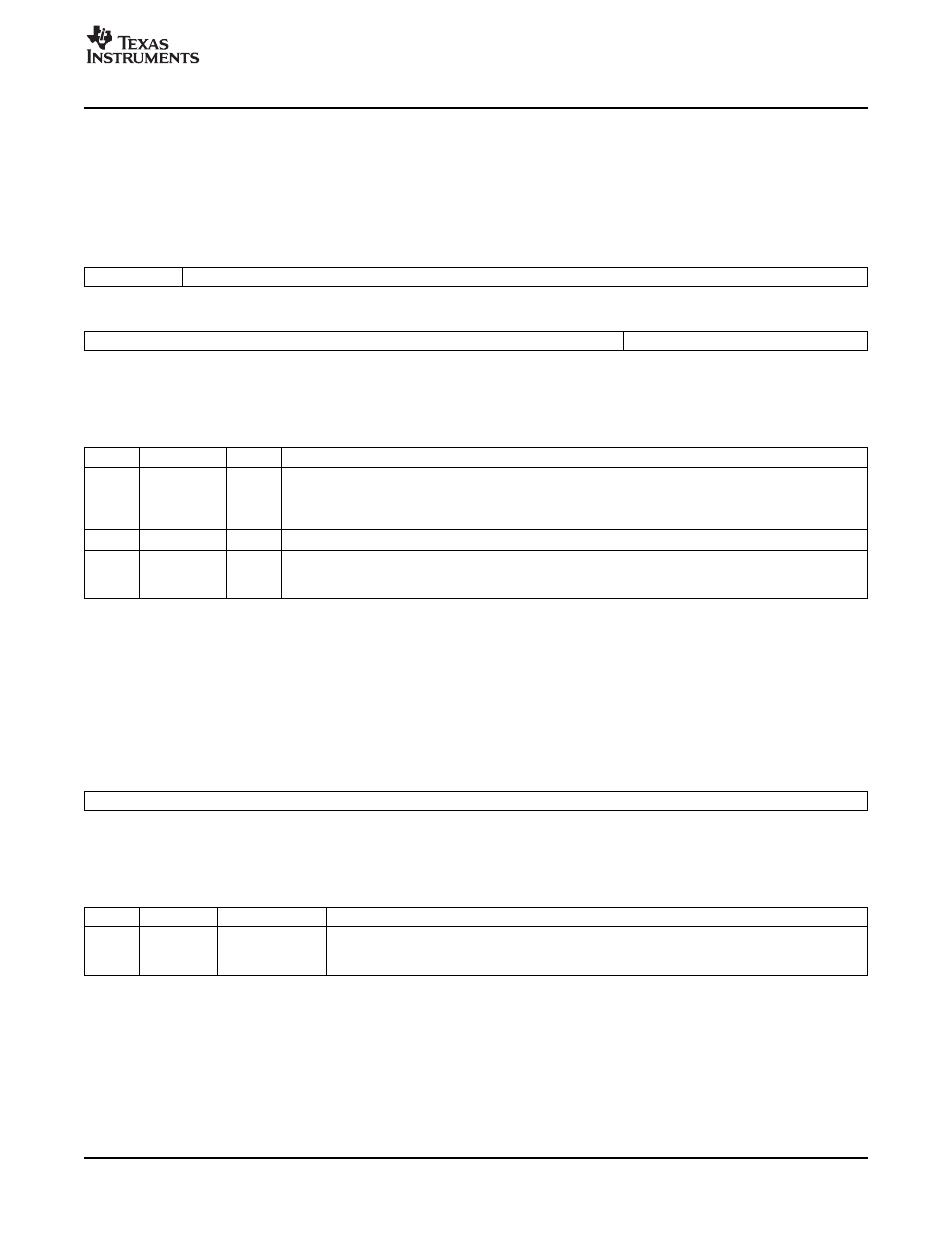

The interrupt priority vector status/clear register (INTPRI) displays the highest priority vector with a

pending interrupt when read. When writing, only bits [4:0] are valid, and the value represents the vector of

the interrupt to be cleared. The INTPRI is shown in

and described in

.

Figure 12. Interrupt Priority Vector Status/Clear Register (INTPRI)

31

30

16

NOINTPEND

Reserved

R-1h

R-0

15

5

4

0

Reserved

INSTAT

R-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 10. Interrupt Priority Vector Status/Clear Register (INTPRI) Field Descriptions

Bit

Field

Value

Description

31

NOINTPEND

Interrupt pending status.

0

Indicates there is a pending interrupt.

1

Indicates that there are no pending interrupts from the interrupt status/clear register.

30-5

Reserved

0

Reserved. Always read as 0. Writes have no effect.

When read, this field displays the vector that is mapped to the highest priority interrupt bit that is

4-0

INSTAT

0-1Fh

pending from the interrupt status/clear register, with bit 0 as the highest priority, and bit 31 as the

lowest. Writing the vector value back to this field clears the interrupt.

The interrupt status/clear register (INTSTATCLR) indicates the unmasked interrupt status. The

INTSTATCLR is shown in

and described in

Figure 13. Interrupt Status/Clear Register (INTSTATCLR)

31

0

INTCLR

R/W-0

LEGEND: R/W = Read/Write; -n = value after reset

Table 11. Interrupt Status/Clear Register (INTSTATCLR) Field Descriptions

Bit

Field

Value

Description

31-0

INTCLR

0-FFFF FFFFh

This field indicates the unmasked status of each interrupt. Writing a 1 to any set bit in this field

clears the corresponding interrupt. If there is a bit set in this register and if the INTLOCAL bit in

the control register (CTRL) is also set, the VLYNQ interrupt (VLQINT) is asserted.

SPRUE36A – September 2007

VLYNQ Port

31