Tnetx4090 thunderswitch ii, Switch – Texas Instruments THUNDERSWITCH II TNETX4090 User Manual

Page 64

TNETX4090

ThunderSWITCH II

9-PORT 100-/1000-MBIT/S ETHERNET

SWITCH

SPWS044E – DECEMBER 1997 – REVISED AUGUST 1999

64

POST OFFICE BOX 655303

•

DALLAS, TEXAS 75265

GMII (port 8)

Figures 18–20 show the timing for the 100-/1000-Mbit/s GMII when operating at 1000 Mbit/s.

Both Mxx_CRS and Mxx_COL are driven asynchronously by the PHY. Mxx_RXD7–MxxRXD0 is driven by the

PHY on the falling edge of Mxx_RCLK. Mxx_RXD7–MxxRXD0 timing must be met during clock periods in which

Mxx_RXDV is asserted. Mxx_RXDV is asserted and deasserted by the PHY on the falling edge of Mxx_RCLK.

Mxx_RXER is driven by the PHY on the falling edge of Mxx_RCLK.

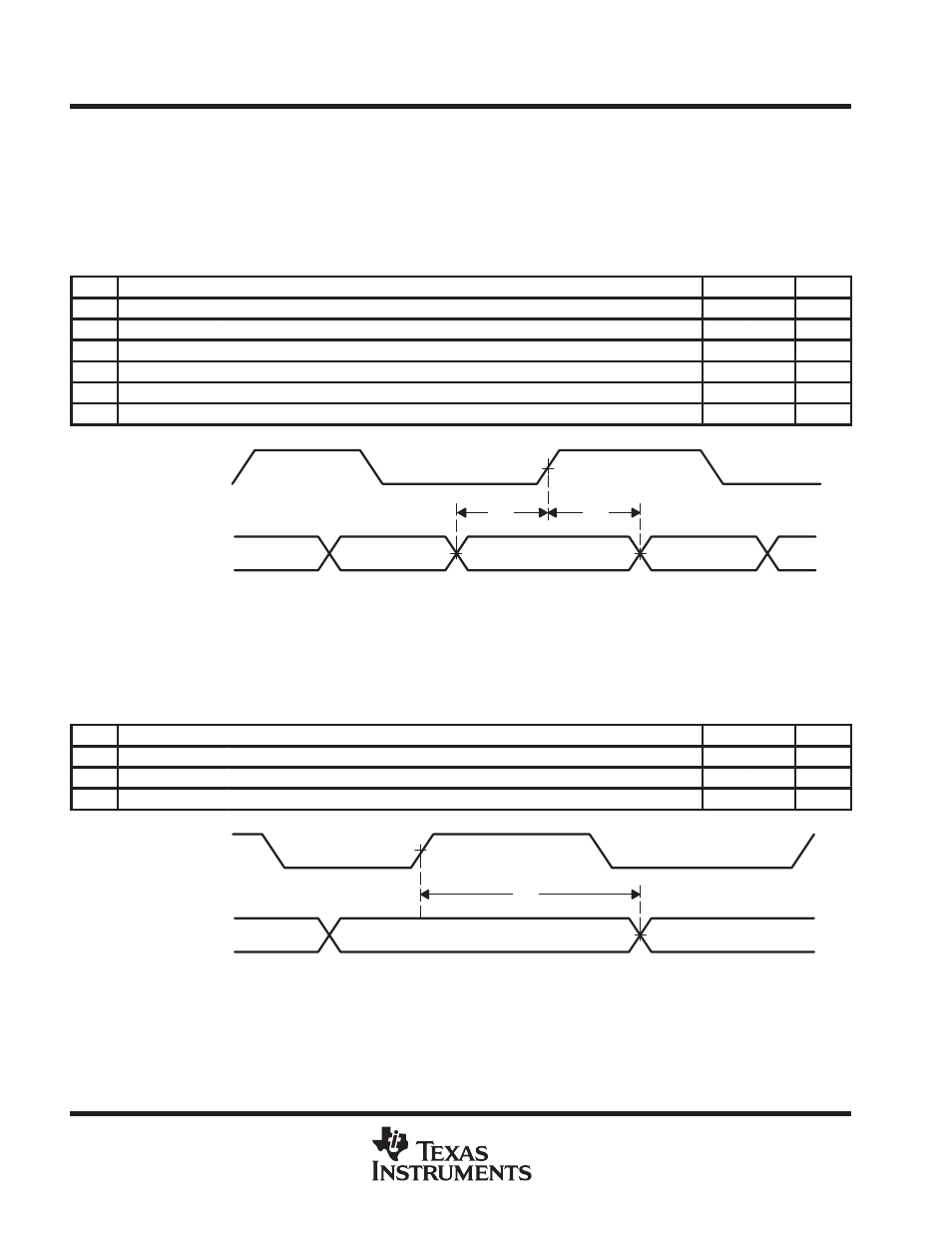

GMII receive (see Figure 18)

NO.

MIN

MAX

UNIT

1

tsu(Mxx_RXD)

Setup time, Mxx_RXD7–Mxx_RXD0 valid before Mxx_RCLK

↑

2

ns

1

tsu(Mxx_RXDV) Setup time, Mxx_RXDV valid before Mxx_RCLK

↑

2

ns

1

tsu(Mxx_RXER) Setup time, Mxx_RXER valid before Mxx_RCLK

↑

2

ns

2

th(Mxx_RXD)

Hold time, Mxx_RXD7–Mxx_RXD0 valid after Mxx_RCLK

↑

1

ns

2

th(Mxx_RXDV)

Hold time, Mxx_RXDV valid after Mxx_RCLK

↑

1

ns

2

th(Mxx_RXER)

Hold time, Mxx_RXER valid after Mxx_RCLK

↑

1

ns

ООООООО

ООООООО

ООООООО

ООООООО

Mxx_RXD7–Mxx_RXD0

Mxx_RXDV

Mxx_RXER

1

2

Mxx_RCLK

Figure 18. GMII Receive

Mxx_CRS and Mxx_COL are driven asynchronously by the PHY. Mxx_GTCLK is derived directly from

Mxx_RFCLK. Mxx_TXD7–Mxx_TXD7 is driven by the reconciliation sublayer synchronous to the Mxx_GTCLK.

Mxx_TXEN is asserted and deasserted by the reconciliation sublayer synchronous to the Mxx_GTCLK rising

edge. Mxx_TXER is driven synchronous to the rising edge of Mxx_GTCLK.

GMII transmit (see Figure 19)

NO.

MIN

MAX

UNIT

1

td(Mxx_TXD)

Delay time, from Mxx_GTCLK

↑

to Mxx_TXD3–MxxTXD0 valid

1.5

4.5

ns

1

td(Mxx_TXEN)

Delay time, from Mxx_GTCLK

↑

to Mxx_TXEN valid

1.5

4.5

ns

1

td(Mxx_TXER)

Delay time, from Mxx_GTCLK

↑

to Mxx_TXER valid

1.5

4.5

ns

ОООООООООООООО

ОООООООООООООО

Mxx_TXD7–Mxx_TXD0

Mxx_TXEN

Mxx_TXER

1

Mxx_GTCLK

Figure 19. GMII Transmit